### 【19】中華民國

#### 【12】專利公報 (B)

【11】證書號數:I448081

【45】公告日: 中華民國 103 (2014) 年 08 月 01 日

[51] Int. Cl.: H03K5/156 (2006.01) H03L7/085 (2006.01)

發明 全6頁

【54】名 稱:全數位時脈校正電路及其方法

【21】申請案號:101102418 【22】申請日:中華民國 101 (2012) 年 01 月 20 日 【11】公開編號:201332293 【43】公開日期:中華民國 102 (2013) 年 08 月 01 日

【72】發 明 人: 鍾菁哲 (TW);沈頌恩 (TW)

【71】申 請 人: 國立中正大學 NATIONAL CHUNG CHENG

UNIVERSITY

嘉義縣民雄鄉大學路 168 號

【74】代理人: 蔡秀玫

【56】參考文獻:

TW 200826506A US 2006/0091921A1

US 2007/0013423A1

H.-J. Hsu, C.-C. Tu, and S.-Y. Huang, "A high-resolution all-digital phase-lock loop with its application to built-in speed grading for memory," in Proc. IEEE Symp. VLSI Design Autom., Apr. 2008, pp. 267-270.

B.-G. Kim, K.-I. Oh, L.-S. Kim, and D.-W. Lee, "A 500MHz DLL with second order duty cycle corrector for low jitter," in Proc. IEEE Custom Integr. Circuits Conf., Jan. 2006, pp. 325-328.

審查人員: 陳臆聰

#### [57]申請專利範圍

- 1. 一種全數位時脈責任週期校正電路,其包含:

- 一取樣單元,其接收並取樣一輸入時脈訊號;

- 一責任週期校正模組,其電性連接該取樣單元,該責任週期校正模組依據該輸入時脈訊 號產生一第一時脈訊號;

- 一鎖相模組,其電性連接該取樣單元與該責任週期校正模組,該鎖相模組依據該第一時脈訊號進行反相處理而產生一第二時脈訊號,該取樣單元傳送該第一時脈訊號與該第二時脈訊號至該鎖相模組,該鎖相模組偵測該第一時脈訊號與該第二時脈訊號之一正緣相位差,以對齊該第一時脈訊號與該第二時脈訊號之正緣相位,該取樣單元傳送已對齊正緣相位之該第一時脈訊號與該第二時脈訊號至該責任週期校正模組,該責任週期校正模組比較該第一時脈訊號與該第二時脈訊號之一脈波寬度差,以調整該第一時脈訊號與第二時脈訊號之脈波寬度直到兩者相等為止,此時將第二時脈訊號輸出為一第三時脈訊號。

- 2. 如申請專利範圍第1項所述之全數位時脈責任週期校正電路,其中該鎖相模組包含:

- 一相位偵測單元,其偵測該正緣相位差,以產生一相位偵測訊號;

- 一相位調整單元,接收該第一時脈訊號與該第二時脈訊號;以及

- 一相位控制單元,電性連接該相位調整單元與該相位偵測單元,依據該相位偵測訊號產生一相位控制碼至該相位調整單元,以驅使該相位調整單元對齊該第一時脈訊號與該第

- 二時脈訊號之正緣相位,該相位控制單元於該第一時脈訊號與該第二時脈訊號相位對齊 後鎖住該相位調整單元。

- 3. 如申請專利範圍第1項所述之全數位時脈責任週期校正電路,其中該責任週期校正模組 包含:

- 一責任週期偵測單元,其依據該第一時脈訊號與該第二時脈訊號之脈波寬度差產生一責任週期偵測訊號;

- 一責任週期調整單元,接收該第一時脈訊號與該第二時脈訊號;以及

- 一責任週期控制單元,電性連接該責任週期校正單元,依據該責任週期偵測訊號產生一責任週期控制碼至該責任週期校正單元,以調整該第一時脈訊號與該第二時脈訊號之脈 波寬度,該責任週期控制單元於調整該第一時脈訊號與該第二時脈訊號之責任週期後鎖 住該責任週期校正單元。

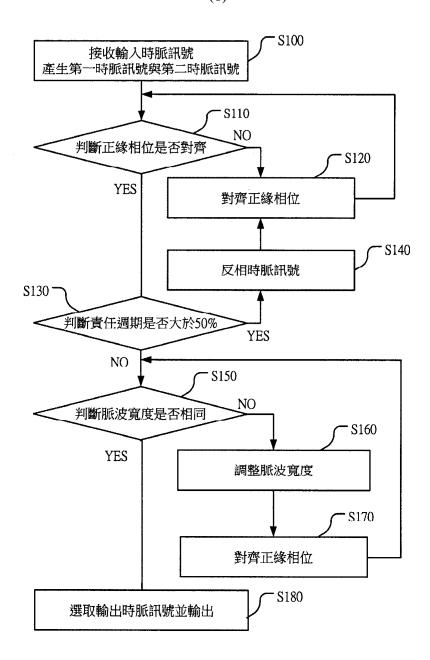

- 4. 一種全數位時脈責任週期校正方法,其包含:

接收一輸入時脈訊號,進行取樣以產生一第一時脈訊號;

進行反相處理以得到一第二時脈訊號;

傳送該第一時脈訊號與該第二時脈訊號至一鎖相模組,以偵測該第一時脈訊號與該第二時脈訊號之正緣相位差,並依據該正緣相位差分別對齊該第一時脈訊號與該第二時脈訊號之正緣相位;

傳送對齊正緣相位後之該第一時脈訊號與該第二時脈訊號至一責任週期校正模組,進行 比較該第一時脈訊號與該第二時脈訊號之脈波寬度差,以調整該第一時脈訊號與第二時 脈訊號之脈波寬度;

傳送該第一時脈訊號與該第二時脈訊號至該鎖相模組,以偵測該第一時脈訊號與該第二時脈訊號之正緣相位差,並依據該正緣相位差分別對齊該第一時脈訊號與該第二時脈訊號之正緣相位;

傳送對齊正緣相位後之該第一時脈訊號與該第二時脈訊號至該責任週期校正模組,進行 比較該第一時脈訊號與該第二時脈訊號之波寬度差,以調整該第一時脈訊號與第二時脈 訊號之脈波寬度;以及

比對該第一時脈訊號與該第二時脈訊號之脈波寬度差為 0 時,輸出該第二時脈訊號為一責任週期為 50% 之全數位時脈訊號。

- 5. 如申請專利範圍第4項所述之全數位責任週期校正方法,其中於偵測該第一時脈訊號與該第二時脈訊號之一第一正緣相位差之步驟中,係偵測該第一正緣相位差產生一相位偵測訊號。

- 6. 如申請專利範圍第 5 項所述之全數位責任週期校正方法,其中於依據該正緣相位差分別 對齊該第一時脈訊號與該第二時脈訊號之正緣相位之步驟中,係依據該相位偵測訊號產 生一相位控制碼至該相位調整單元,以補償該正緣相位差。

- 7. 如申請專利範圍第4項所述之全數位責任週期校正方法,其中於比較該第一時脈訊號與該第二時脈訊號之脈波寬度差之步驟中,係依據該第一時脈訊號與該第二時脈訊號之一脈波寬度差產生一責任週期偵測訊號。

- 8. 如申請專利範圍第7項所述之全數位責任週期校正方法,其中於調整該第一時脈訊號與 第二時賣訊號之脈波寬度之步驟中,係依據該責任週期偵測訊號產生一責任週期控制碼 至該責任週期校正單元,以調整該第一時脈訊號與該第二時脈訊號之脈波寬度。

#### 圖式簡單說明

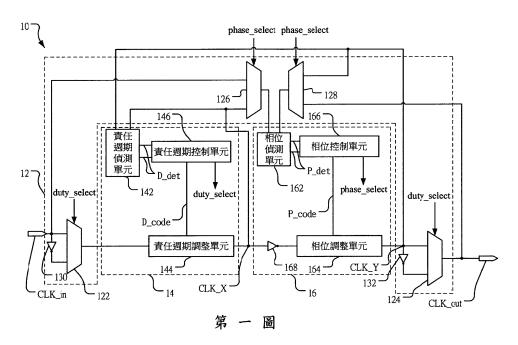

第一圖為本發明之一實施例之電路圖;

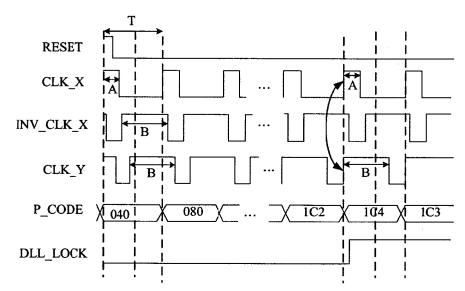

第二 A 圖與第二 B 圖為本發明之一實施例之波形圖;

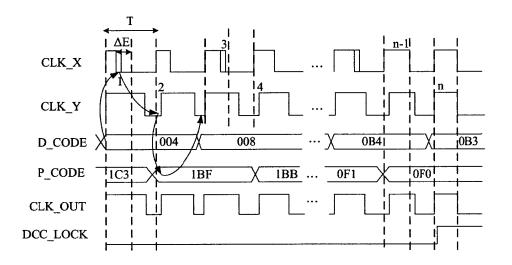

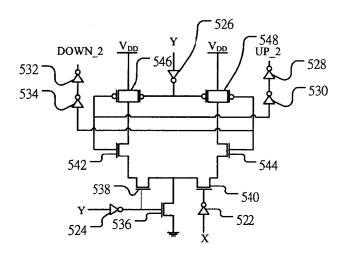

第三圖為本發明之粗調相位偵測電路的電路圖;

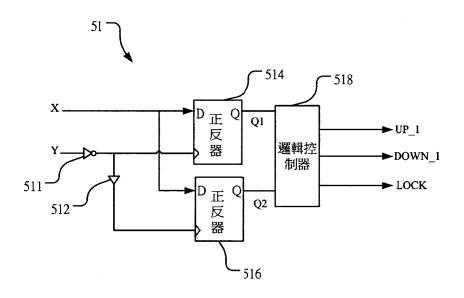

第四圖為本發明之微調相位偵測電路的電路圖;以及 第五圖為本發明之一實施例之流程圖。

第二A圓

## 第二日圖

第三圖

# 第四圖

第五圖