# 國 立 交 通 大 學 電子工程學系電子研究所

博士論文

應用於系統晶片設計之 自動化合成時序鎖定迴路 Automatic Synthesis of Timing-Locked Loops for SoC Designs

研究生:鍾菁哲

指導教授:李鎮宜

中華民國 九十二 年 十 月

## 應用於系統晶片設計之自動化合成時序鎖定迴路

Automatic Synthesis of Timing-Locked Loops for SoC Designs

研究生: 鍾菁哲Student : Ching-Che Chung指導教授: 李 鎮 宜 博士Advisor : Dr. Chen-Yi Lee

國立交通大學

電子工程學系電子研究所

博士論文

A Dissertation

Submitted to Institute of Electronics College of Electrical Engineering and Computer Science National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in

**Electronics Engineering**

October 2003

Hsinchu, Taiwan, Republic of China.

中華民國 九十二 年 十 月

函

主旨:推薦電子工程學系博士班研究生鍾菁哲,舉行博士班學位口試。

- 說明:本人所指導之博士班學生鍾菁哲,業已通過資格考試,並完成本校電子工 程學系電子研究所博士班規定之學科課程及論文研究訓練。鍾君主要從事 全數位鎖相迴路(ADPLL)及全數位延遲鎖相迴路(ADDLL)之研究工作,其 論文題目「應用於系統晶片設計之自動化合成時序鎖定迴路」(Automatic Synthesis of Timing-Locked Loops for SoC Designs)針對 ADPLL/ADDLL 在不同應用或規格上的需求,從晶片性能、面積及功率消耗三方面著手, 提出一系列的系統化設計方法和晶片實現方式,並透過矽晶片驗證所改善 效能。相關研究成果如下:

- Jing-Jer Jong and Chen-Yi Lee, "A Novel Structure for Portable Digitally Controlled Oscillator," in *IEEE International Symposium on Circuits and Systems*, Vol. 1, pp. 272-275, May 2001.

- [2] <u>Ching-Che Chung</u> and Chen-Yi Lee, "An all-digital phase-locked loop for high-speed clock generation," in *IEEE International Symposium on Circuits and Systems*, Vol. 3, pp. 26-29, May 2002.

- [3] Hsie-Chia Chang, <u>Ching-Che Chung</u>, Chien-Ching Lin, and Chen-Yi Lee, "A 300 MHz Reed-Solomon decoder chip using inverionless decomposed architecture for Euclidean algorithm, " in 28<sup>th</sup> European Solid-State Circuits Conf. (ESSCIRC), Florence, Italy, Sep. 2002.

- [4] <u>Ching-Che Chung</u> and Chen-Yi Lee, "An all-digital phase-locked loop for high-speed clock generation," in *IEEE Journal of Solid-State Circuits*, Vol. 38, pp.347-351, Feb. 2003.

- [5] <u>Ching-Che Chung</u> and Chen-Yi Lee, "A new DLL-based approach for all-digital multi-phase clock generation, " accepted by *IEEE Journal of Solid-State Circuits*.

投出待審之論文:

[6] <u>Ching-Che Chung</u> and Chen-Yi Lee, "An All-Digital Fast-Locking DLL for Wide-Range Clock Deskew Applications," submitted to *IEICE Transactions on Electronics*. 目前尚有一篇期刊論文正在審查當中。除此之外,鍾君曾參與多項業界之 產學合作計畫,並在 86 學年度大學校院積體電路設計競賽 Cell-based 組,獲得第三名的佳績。目前正與學弟們從事無線網路系統的設計及相關 研究。

總言之,鍾君在過去的研究期間,已滿足本所在課業及研究上的要求,並在團隊研究方面,獲致肯定,因此特以推薦之。

推薦人

國立交通大學 電子工程學系 教授

中華民國九十二年九月

# 國立交通大學

## 論文口試委員會審定書

本校電子工程學系電子研究所博士班\_ 鐘菁哲 君 所提論文 應用於系統晶片設計之自動化合成時序鎖相迴路 合於博士資格標準、業經本委員會評審認可。

EX.

暂

trans

| 口試委員:    | 他建了。       | 黄威  |

|----------|------------|-----|

|          | 任建藏        | 黄 威 |

|          | 徐舜氏        | 之進  |

|          | 徐爵民        | 王進賢 |

|          | & the size | 刻痘  |

| 0.980    | 吴介琮        | 劉濱達 |

| t de set | 是的之        |     |

|          | 吳 誠 文      |     |

| RAZZ | 教授   |

|------|------|

|      | RAZZ |

九十二 民國 年 + 月 日 菈

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University Hsinchu, Taiwan, R.O.C.

Date : 2003-10-01

We have carefully read the dissertation entitled <u>Automatic Synthesis of</u> <u>Timing-Locked Loops for SoC Designs</u>

submitted by Ching-Che Chung in partial fulfillment of the requirements of

the degree of DOCTOR OF PHILOSOPHY and recommend its acceptance.

hein-h Chein-Wei Jen

Jyuo-Min Shyu

SORIE Jieh-Tsorng Wu Cheng-Wen Wu

Wei Hwang Jine Shyan Wang

Bin-Da Liu

Thesis Advisor : en-Yi Lee

Director

Pau- loc Sau-Gee Chen

Chairman 'i Lee

## 博碩士論文電子檔案上網授權書

(提供授權人裝釘於紙本論文書名頁之次頁用)

本授權書所授權之論文爲授權人在國立交通大學電子工程系 92 學年度 第一學期取得博士學位之論文。

論文題目:應用於系統晶片設計之自動化合成時序鎖定迴路 指導教授:<u>李鎭宜</u>

茲同意將授權人擁有著作權之上列論文全文(含摘要),非專屬、無償 授權國家圖書館及本人畢業學校圖書館,不限地域、時間與次數,以微 縮、光碟或其他各種數位化方式將上列論文重製,並得將數位化之上列 論文及論文電子檔以上載網路方式,提供讀者基於個人非營利性質之線 上檢索、閱覽、下載或列印。

讀者基於非營利性質之線上檢索、閱覽、下載或列印上列論文,應依著作權法 相關規定辦理。

授權人: 鍾菁哲

簽名: 鉅

· 中華民國 92 年 10 月 3 日

### 用於系統晶片設計之自動化合成時序鎖定迴路

研究生: 鍾菁哲

指導教授:李鎮宜博士

國立交通大學電子工程學系電子研究所

#### 摘要

在此論文中,我們針對全數位鎖相迴路及全數位延遲鎖相迴路的設計,提出 了有彈性的架構,以便可迅速配合不同應用領域進行修改。本論文所提出的架構 可有效的縮減迴路鎖定所需的時間,並且在配合所提出的自動化合成技術下,使 用數位積體電路技術和標準元件庫,可在短時間內快速的合成使用者所需求的全 數位鎖相迴路或是全數位延遲鎖相迴路。因此本論文所提出的架構和自動化設計 方法,非常適合應用於系統晶片使用。

此論文首先提出如何克服標準元件庫的限制來提高延遲元件的解析度和相位 頻率比較器的靈敏度。接著本論文所提出的微調延遲元件和相位比較器便被應用 到全數位鎖相迴路及全數位延遲鎖相迴路的設計。時間數位量測轉換器被大量的 應用在所提出的全數位鎖相迴路及全數位延遲鎖相迴路的設計裡,以減少頻率鎖 定和相位鎖定所需的時間。接著本論文提出以延遲鎖相迴路架構為基礎的全數位 多相位時脈產生器,在此多相位時脈產生器的設計上,時間數位量測轉換器用來 選定適當的延遲範圍,以避免產生傳統電路設計會鎖定到諧波的困擾。

最後本論文提出了合成全數位鎖相迴路、全數位延遲鎖相迴路及全數位多相 位時脈產生器的方法。因而全數位鎖相迴路、全數位延遲鎖相迴路及全數位多相 位時脈產生器的邏輯閘層次設計電路,將可以使用標準元件庫來自動產生。也因 此針對全數位鎖相迴路、全數位延遲鎖相迴路及全數位多相位時脈產生器所需的 設計時間和設計複雜度都可以因此大幅度的降低。

# Automatic Synthesis of Timing-Locked Loops for SoC Designs

Student : Ching-Che Chung

Advisor : Dr. Chen-Yi Lee

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

### Abstract

In this dissertation, the designs for All-Digital Phase-Locked Loop (ADPLL) and All-Digital Delay-Locked Loop (ADDLL) are presented. The proposed flexible ADPLL/ADDLL architectures can easily be modified to fit different applications and achieve fast lock-in time. The proposed automated synthesis methodology uses both benefits of digital VSLI and cell-based design to build up user-specified ADPLL/ADDLL in a short time, making it very suitable for System-on-Chip (SoC) applications.

This dissertation first presents a scheme to overcome the limitations of standard cells and to build up high resolution delay cell and high sensitivity Phase and Frequency detector (PFD). Then the proposed fine-tuning delay cell and PFD are applied to ADPLL/ADDLL. Time-to-Digital Converter (TDC) is widely used in the proposed ADPLL/ADDLL architecture to reduce frequency/phase acquisition time. Then design for the proposed DLL-based All-Digital Multi-phase Clock Generator (ADMCG) is presented. In ADMCG design, TDC is used to choose a suitable delay range to avoid false-lock to harmonics.

Finally, a synthesis approach for ADPLL/ADDLL/ADMCG design is presented. As a result, the gate-level Hardware Description Language (HDL) codes of ADPLL/ADDLL/ADMCG can be automatically generated using standard cells from cell-library. Hence both design time and design complexity of ADPLL/ ADDLL/ADMCG is greatly reduced by the proposed methodology.

# Acknowledgments

I would like to express my deepest gratitude to my advisor Prof. Chen-Yi Lee for his sophomore enthusiastic guidance and encouragement throughout the research, and wholeheartedly give him and his family my best wishes.

During my research, I would like to thank National Science Council (NSC) for supporting the project of My Ph. D work. The chip support from Chip Implementation Center (CIC) of NSC is acknowledged, too.

I want to thank my senior Si2 group mate, Dr. Terng-Yin Hsu and Mr. Terng-Ren Hsu for many valuable discussions and great help. Besides, I much appreciate my junior Mr. Hsuan-Yu Liu and Mr. Chien-Ching Lin for their comments and CAD supporting. I also want to thank all members of the Si2 group of NCTU for plenty of fruitful assistance in my graduated lives.

Finally, I give the greatest respect and love to my family and my girl friend, JoJo Ho, and I want to express my highest appreciation for their support and understanding. This thesis is dedicated to them for assisting me to achieve the most important stage in my life. I never let them down and hope them happy forever.

# Contents

| Chapter | 1 Introduction                                            | 1  |

|---------|-----------------------------------------------------------|----|

| 1.1     | Motivation                                                | 1  |

| 1.2     | Thesis Organization                                       | 3  |

| Chapter | 2 Timing Critical Modules in ADPLL and ADDLL Architecture | 6  |

| 2.1     | Design of High Resolution Delay Cells                     | 7  |

| 2.2     | High Sensitivity Phase and Frequency Detector Deign       | 11 |

| 2.3     | Summary                                                   | 15 |

| Chapter | 3 All-Digital Phase-Locked Loop Design                    | 16 |

| 3.1     | Overview of Phase-Locked Loop (PLL)                       | 17 |

| 3.2     | Design Trade-Off in Different PLL Architectures           | 21 |

| 3.3     | The proposed ADPLL Architecture                           | 23 |

| 3.3.    | 1 ADPLL Architecture Overview                             | 23 |

| 3.3.    | 2 Design for Binary Search ADPLL Controller               | 25 |

| 3.3.    | 3 Design for TDC-Based Fast-Locking ADPLL Controller      | 26 |

| 3.4     | The ADPLL Circuit Design                                  | 29 |

| 3.4.    | 1 Design for Digital-Controlled Oscillator                | 29 |

| 3.4.    | 2 Design for Phase and Frequency Detector                 | 31 |

| 3.4.    | 3 Loop Filter Design                                      | 31 |

| 3.4.    | 4 A Systematic Approach for ADPLL Design                  | 32 |

| 3.5     | Experimental Results for the ADPLL test chip              | 33 |

| 3.6     | Summary                                                   | 37 |

| Chapter | 4 All-Digital Delay-Locked Loop Design                    | 38 |

| 4.1     | Overview of Delay-Locked Loop (DLL)                       | 40 |

| 4.1     | Design Trade-Off in Different DLL Architectures           | 42 |

| 4.2     | The proposed ADDLL Architecture                           | 45 |

| 4.3       | The ADDLL Circuit Design                       | 50 |

|-----------|------------------------------------------------|----|

| 4.4 I     | Experimental Results for the ADDLL test chip   | 53 |

| 4.5 \$    | Summary                                        | 59 |

| Chapter 5 | All-Digital Multi-Phase Clock Generator Design | 60 |

| 5.1       | The proposed ADMCG architecture                | 62 |

| 5.2       | ADMCG Test Chip Design                         | 67 |

| 5.3 I     | Experimental Results for the ADMCG Test Chip   | 69 |

| 5.4 \$    | Summary                                        | 73 |

| Chapter 6 | Automated Synthesis of ADPLL, ADDLL, and ADMCG | 74 |

|           | for SoC Applications                           |    |

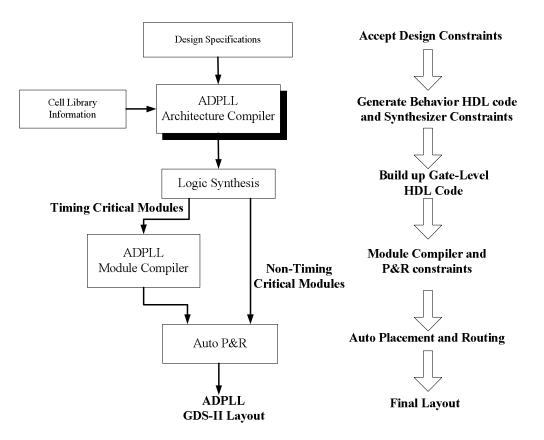

| 6.1       | Automated ADPLL Synthesis                      | 75 |

| 6.1.1     | Cell Library Data Preparation                  | 75 |

| 6.1.2     | ADPLL Architecture Compiler                    | 76 |

| 6.1.3     | Automated ADPLL Synthesis Flow                 | 78 |

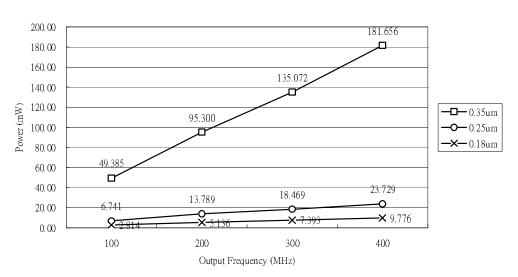

| 6.1.4     | Implementations Results                        | 81 |

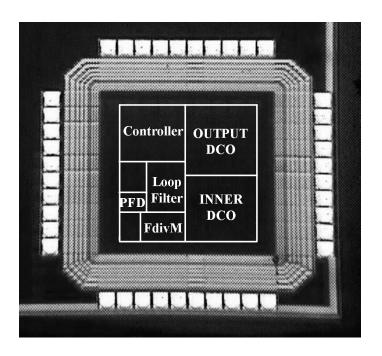

| 6.1.5     | Test Chip Measurement Results                  | 83 |

| 6.1.6     | Summary                                        | 85 |

| 6.2       | Automated ADDLL Synthesis                      | 86 |

| 6.2.1     | Cell Library Data Preparation                  | 86 |

| 6.2.2     | ADDLL Architecture Compiler                    | 87 |

| 6.2.3     | Automated ADDLL Synthesis Flow                 | 89 |

| 6.3       | Automated ADMCG Synthesis                      | 90 |

| 6.3.1     | Cell Library Data Preparation                  | 90 |

| 6.3.2     | ADMCG Architecture Compiler                    | 90 |

| 6.3.3     | Automated ADMCG Synthesis Flow                 | 92 |

| 6.4 \$    | Summary                                        | 93 |

| Chapter 7 | Conclusions and Future Works                   | 94 |

### Reference

97

# **List of Figures**

| Fig        | 2.1        | The schematic of the proposed delay cell                                      | 8        |

|------------|------------|-------------------------------------------------------------------------------|----------|

| Fig        | 2.2        | The CMOS circuit of the proposed delay cell.                                  | 8        |

| Fig        | 2.3        | The proposed high resolution delay cell                                       | 9        |

| Fig        | 2.4        | The sample-based phase detector.                                              | 11       |

| Fig        | 2.5        | The proposed high sensitivity phase and frequency detector                    | 12       |

| Fig        | 2.6        | The simulation waveform of the proposed PFD                                   | 13       |

| Fig        | 2.7        | The digital pulse amplifier.                                                  | 14       |

| Fig        | 2.8        | The SPICE simulation waveform of the digital pulse amplifier                  | 14       |

| Fig.       | 3.1:       | The general PLL architecture                                                  | 18       |

| Fig.       | 3.2:       | The frequency acquisition process of PLL                                      | 19       |

| Fig        | 3.3:       | The phase acquisition process of PLL.                                         | 20       |

| Fig        | 3.4        | The proposed ADPLL architecture                                               | 24       |

| Fig        | 3.5        | The Binary search ADPLL controller.                                           | 26       |

| Fig        | 3.6        | The structure of the proposed TDC for fast-locking                            | 27       |

|            |            | ADPLL                                                                         |          |

| Fig        | 3.7        | The proposed cell-based DCO architecture.                                     | 29       |

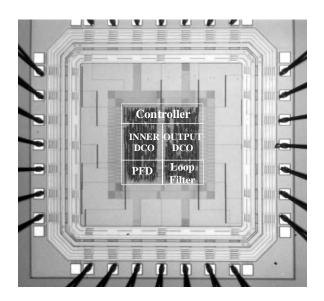

| Fig        | 3.8        | Microphotograph of the ADPLL (TSMC 0.35um).                                   | 32       |

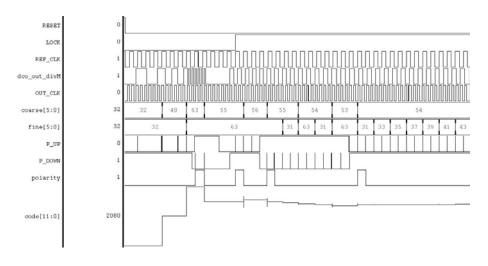

| Fig        | 3.9        | Transient response of the binary search ADPLL (@200MHz)                       | 33       |

| Fig        | 3.10       | Transient response of TDC-based fast-locking ADPLL (@300MHz)                  | 34       |

| Fig        | 3.11       | Compared TDC-based ADPLL to binary search ADPLL (@300MHz)                     | 35       |

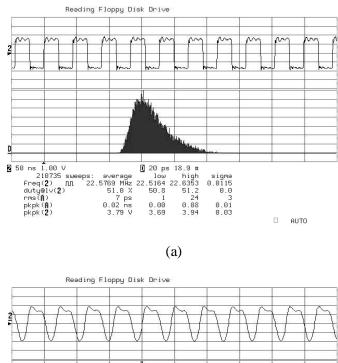

| Fig        | 3.12       | Jitter histogram of the ADPLL (a) at 45MHz (b) at 450MHz                      | 36       |

| Fig        | 4.1        | Concept of Clock Deskew.                                                      | 39       |

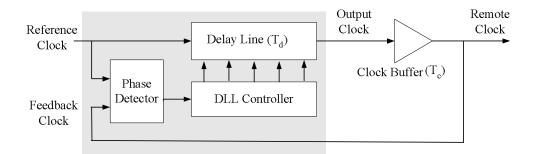

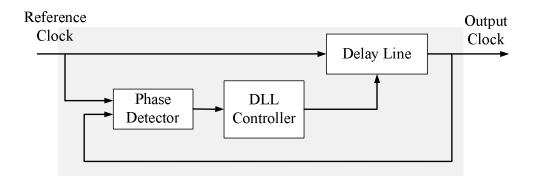

| Fig.       | 4.2:       | The general DLL architecture.                                                 | 40       |

| Fig        | 4.3        | The phase acquisition process of DLL.                                         | 41       |

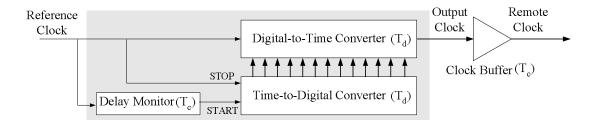

| Fig        | 4.4        | Fast-Locking DLL based on TDC-DTC architecture.                               | 44       |

| Fig        |            |                                                                               |          |

|            | 4.5        | The proposed fast-locking wide-range DLL.                                     | 45       |

| Fig        | 4.5<br>4.6 | The proposed fast-locking wide-range DLL.      Initial phase error estimator. | 45<br>46 |

| Fig<br>Fig | 4.6        |                                                                               |          |

| Fig | 4.9  | (a) Fine-tuning delay cell (b) Fine-tuning delay cell with disable control (c)   |    |

|-----|------|----------------------------------------------------------------------------------|----|

|     |      | Coarse-tuning delay cell.                                                        | 50 |

| Fig | 4.10 | Simulation waveform of DCDL (a) at 50MHz clock input (b) at 500MHz               |    |

|     |      | clock input                                                                      | 52 |

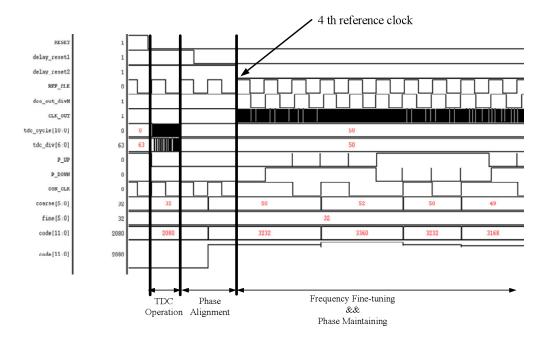

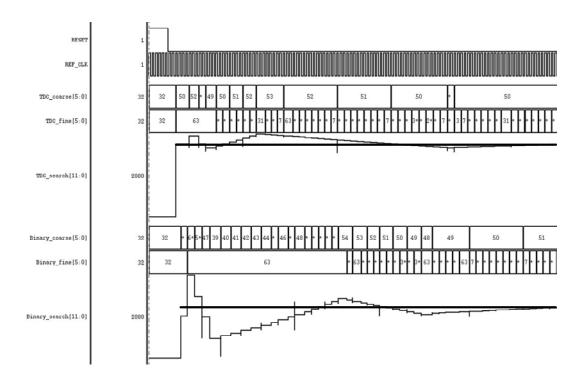

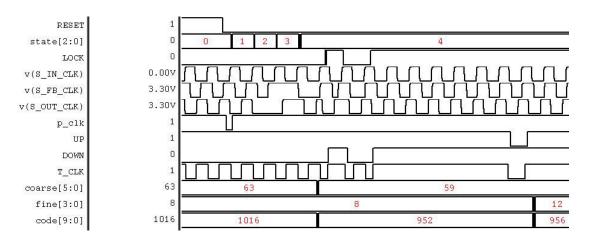

| Fig | 4.11 | Transient response of the proposed ADDLL.                                        | 54 |

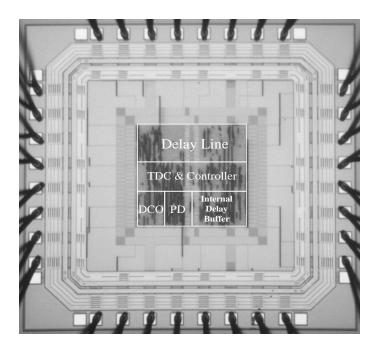

| Fig | 4.12 | Microphotograph of the DLL test chip                                             | 54 |

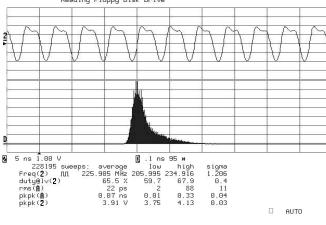

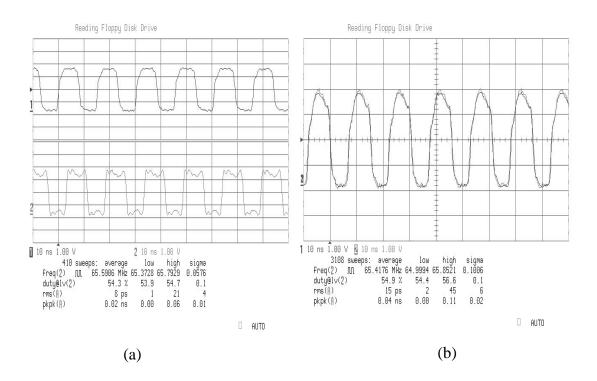

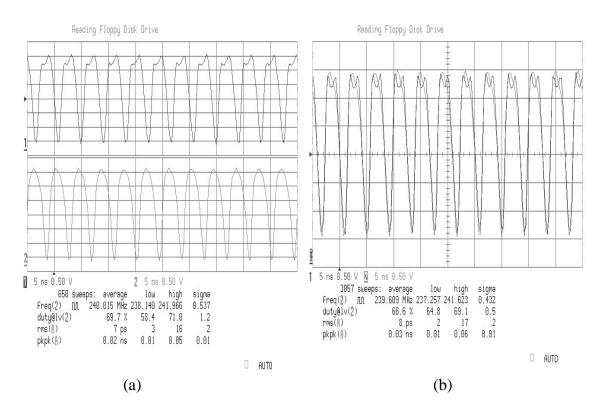

| Fig | 4.13 | Measured jitter at 65MHz. (a) DLL is reset (b) DLL is locked                     | 55 |

| Fig | 4.14 | Measured jitter at 487MHz. (a) DLL is reset (b) DLL is locked                    | 56 |

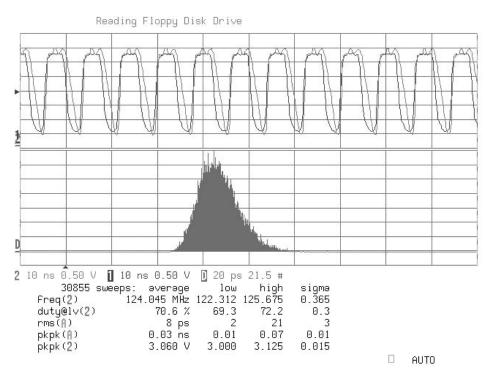

| Fig | 4.15 | Measured long-term jitter histogram (at 125MHz)                                  | 57 |

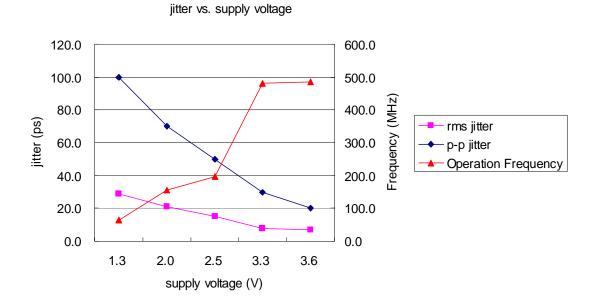

| Fig | 4.16 | Measured jitter and frequency vs. supply voltage                                 | 57 |

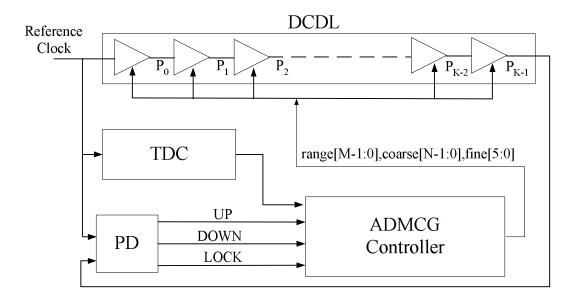

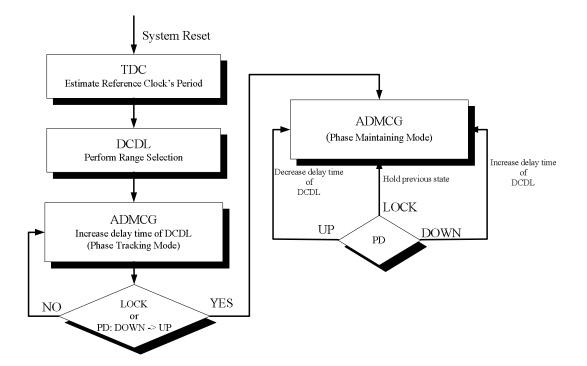

| Fig | 5.1  | The proposed ADMCG architecture.                                                 | 62 |

| Fig | 5.2  | The proposed ADMCG control algorithm.                                            | 63 |

| Fig | 5.3  | The proposed Time-to-Digital Converter (TDC) for multi-clock generator           | 64 |

| Fig | 5.4  | The architecture of one delay stage                                              | 66 |

| Fig | 5.5  | The proposed 7:1 data channel compression transceiver (a) Transmitter            |    |

|     |      | (b)Receiver                                                                      | 68 |

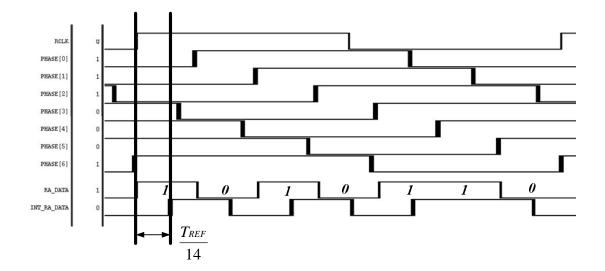

| Fig | 5.6  | The transient response of the ADMCG (at 85MHz).                                  | 69 |

| Fig | 5.7  | The post-layout simulation of the receiver (at 85MHz)                            | 70 |

| Fig | 5.8  | Measured multi-phase clock signals (at 32MHz).                                   | 71 |

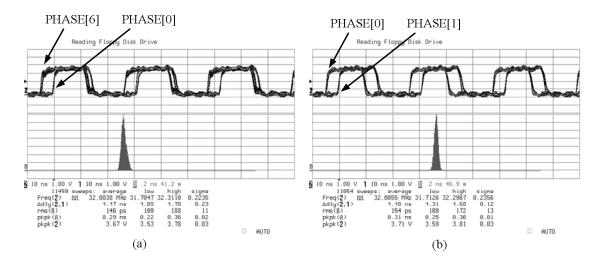

| Fig | 5.9  | Measured long-term jitter histogram of the transmitted data (at 32MHz). $\ldots$ | 72 |

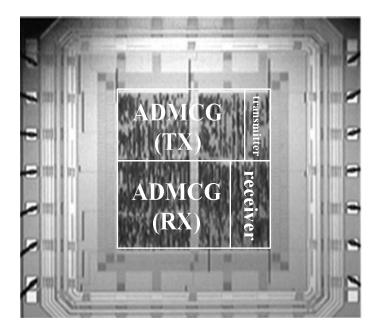

| Fig | 5.10 | Microphotograph of the ADMCG test chip                                           | 73 |

| Fig | 6.1  | The proposed automated ADPLL synthesis flow.                                     | 79 |

| Fig | 6.2  | The interconnection RC effects.                                                  | 80 |

| Fig | 6.3  | Power Consumption of the ADPLL for different processes.                          | 82 |

| Fig | 6.4  | Microphotograph of the ADPLL (UMC 0.18um).                                       | 83 |

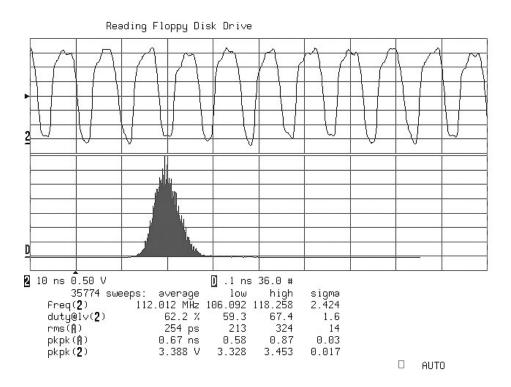

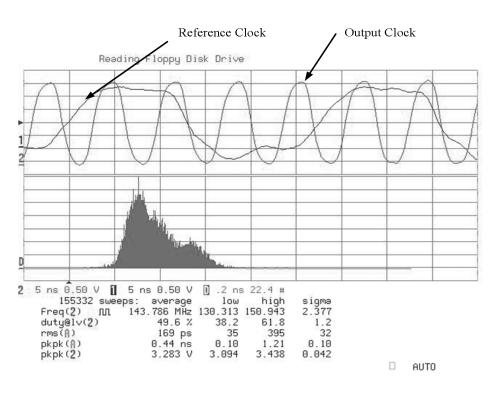

| Fig | 6.5  | Measured long-term jitter histogram of in-phase clock output (at 144MHz).        | 84 |

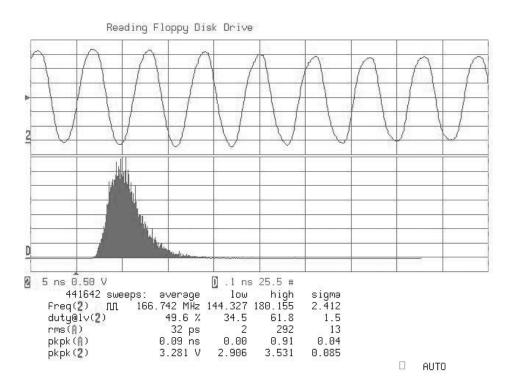

| Fig | 6.6  | Measured long-term jitter histogram of average clock output (at 166MHz)          | 85 |

# List of Tables

| 2.1: | CONTROL CODE VS. DELAY TIME OF THE PROPOSED DELAY                                                                   |                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | CELL                                                                                                                | 10                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|      |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 3.1: | PLL PERFORMANCE                                                                                                     | 37                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|      | COMPARISONS                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 4.1  | PERFORMANCE SUMMARY OF THE PROPOSED DLL                                                                             | 58                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 4.2  | DLL PERFORMANCE COMPARISONS                                                                                         | 58                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6.1  | The ADPLL SPECIFICATIONS                                                                                            | 77                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6.2  | DCO OUTPUT FREQUENCY RANGE FOR DIFFERENT                                                                            |                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|      | PROCESSES                                                                                                           | 81                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6.3  | ADPLL AREA INFORMATION FOR DIFFERENT PROCESSES                                                                      | 81                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6.4  | The ADPLL TEST CHIP SPECIFICATIONS.                                                                                 | 84                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6.5  | The ADDLL SPECIFICATIONS.                                                                                           | 87                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6.6  | The ADMCG SPECIFICATIONS.                                                                                           | 91                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|      | <ul> <li>3.1:</li> <li>4.1</li> <li>4.2</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | <ul> <li>3.1: PLL PERFORMANCE</li> <li>COMPARISONS.</li> <li>4.1 PERFORMANCE SUMMARY OF THE PROPOSED DLL.</li> <li>4.2 DLL PERFORMANCE COMPARISONS.</li> <li>6.1 The ADPLL SPECIFICATIONS.</li> <li>6.2 DCO OUTPUT FREQUENCY RANGE FOR DIFFERENT</li> <li>PROCESSES.</li> <li>6.3 ADPLL AREA INFORMATION FOR DIFFERENT PROCESSES.</li> <li>6.4 The ADPLL TEST CHIP SPECIFICATIONS.</li> </ul> |  |  |

# Chapter 1 Introduction

### **1.1 Motivation**

As VLSI technology grows up rapidly, the design trend goes toward system-level integration and single-chip solution. The system-level design considerations can lead to more cost-effective realizations, but it also results in more design complexity and design efforts. However, the design cycle remains the same or even shorter due to the time-to-market issue. Thus in System-On-Chip (SoC) designs, each module should better be reusable and process portable, so that total design time of SoC can be reduced. Unfortunately, some timing critical blocks, such as: Phase-Locked Loops (PLLs) and Delay-Locked Loops (DLLs) often are not reusable and process portable.

PLL and DLL are widely used in SoC designs. They are often applied to communication applications, such as: frequency synthesizer, clock multiplier, Clock and Data Recovery (CDR) circuit, and clock de-skew applications. They are very essential for current SoC designs, and for different modules, they may have different design specifications or requirements for PLLs and DLLs. As a result, how to design these PLLs/DLLs in a more efficient way becomes more and more important in these days.

For example, in single chip cable modem residential gateway [47], there are seven PLLs and over one hundred internally generated clocks used in this single chip gateway. Thus how to design these PLLs in an efficient way becomes very important for reducing system turn around time. And the importance to develop a systematic PLL/DLL design approach is required in current SoC era.

The design of PLL/DLL is a trade-off among jitter performance, frequency / phase resolution, lock-in time, area cost, power consumption, circuit complexity and design time. It is hard to design one PLL/DLL suitable for all applications. It often needs to redesign the PLL/DLL for target applications. If a wide-range PLL/DLL is designed for SoC applications, it can be used in more modules without modify it. But this scheme may waste unnecessary area cost and power consumption due to the requirement for wide-range operation. Thus a systematic design methodology to design user-specified PLLs/DLLs in a short time is necessarily for current SoC designs.

All-digital and cell-based approach is preferred for SoC applications. It can reduce both design time and design complexity for PLL/DLL. And this approach is also suitable for automated synthesis of All-Digital Phase-Locked Loop (ADPLL) and All-Digital Delay-Locked Loop (ADDLL).

However, due to the limitations of cell-based design, it is difficult to design a low-jitter, low-power, and high resolution ADPLL/ADDLL. Thus how to overcome the limitations of standard cells to build up a high resolution delay cell and high sensitivity frequency/phase detector (PFD) are the important design challenges for our research.

In this thesis, we propose the flexible ADPLL/ADDLL architectures for a truly portable and cost-effective ADPLL/ADDLL [35] solution. And we explain the proposed scheme to overcome the limitations of the standard cells and to build up high resolution delay cell and high sensitivity phase detector.

Time-to-Digital Converter (TDC) is widely used in the proposed ADPLL/ADDLL architecture to reduce frequency/phase acquisition time and achieve fast lock-in time. In all-digital multi-phase clock generator (ADMCG) [46], it is used to choose a suitable delay range to avoid false-lock to harmonics.

In this thesis, an automated synthesis methodology for ADPLL/ADDLL/ADMCG design is presented. Thus these modules now can be automatically generated using standard cells from cell-library. As a result, the proposed methodology uses both benefits of digital VLSI and cell-based design to build up user-specified ADPLL/ADDLL/ADMCG in a short time, and reduces design time and design complexity of ADPLL/ADDLL/ADMCG, making it very suitable for System-On-Chip (SoC) applications.

### **1.2 Thesis Organization**

In this dissertation, we focus on algorithms, architectures, and circuits of high performance, low power, and area efficient ADPLL/ADDLL/ADMCG designs. And for SoC applications, we proposed an automated synthesis methodology to take design specifications and automatically generate the gate-level netlist for ADPLL/ADDLL/ADMCG. The proposed methodology can greatly reduce design time and design complexity of these modules in SoC era.

In chapter 2, we present the common timing critical modules design for ADPLL/ADDLL /ADMCG. The resolution of delay cell and the sensitivity of PFD have large influences on the jitter performance of the output clock, and they also have large effects on the final frequency error or phase error. In this chapter, we explain the proposed scheme to overcome the

limitations of the standard cells and to build up high resolution delay cell and high sensitivity phase detector.

In chapter 3, the design for all-digital phase-locked loop (ADPLL) is presented. To reduce the system turn around time for SoC design, the ADPLL using the proposed high resolution delay cell and the proposed high sensitivity PFD is presented. The proposed ADPLL controller can achieve fast lock-in time, and the proposed delay cell can reduce both cost and design time for building a high resolution cell-based DCO. And the proposed PFD can improve the jitter performance and reduce the frequency error for the output clock. Moreover the flexible ADPLL architectures for different target applications are presented in this chapter for a truly portable and cost-effective ADPLL-based frequency synthesizer solution.

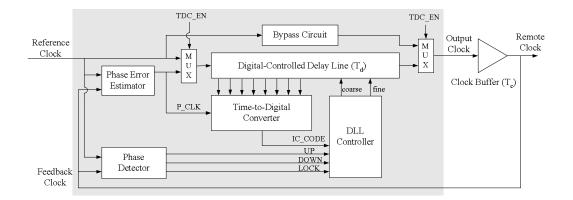

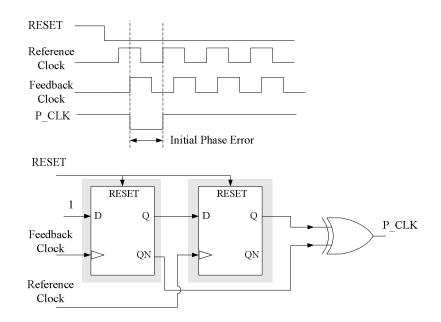

In chapter 4, the design for all-digital delay-locked loop (ADDLL) is presented. As the speed and the complexity of VLSI system increases rapidly, clock skew and clock jitter effects become more and more important now. It is difficult to design a DLL to overcome total effects caused by process, voltage, temperature, and loading (PVTL) variations. As in conventional DLL, the operation range of DLL is very limited. In this chapter, we propose an all-digital fast-locking DLL. The proposed DLL utilizes Time-to-Digital Converter (TDC) circuit and Digital-to-Time Converter (DTC) circuit to complete coarse-tuning in one clock cycle, resulting in less lock-in time. And the area cost for TDC and DTC can be shared with delay line. The proposed Digital-Controlled Delay Line (DCDL) architecture can turn off unused delay cells at high frequency operation, thus it is very suitable for wide-range clock deskew applications demanded in system-level integration.

In chapter 5, the design for an all-digital multi-phase clock generator (ADMCG) is presented. Multi-phase clocks are useful in many applications to process data streams at the

bit rate higher than internal clock frequencies. But there are two problems of conventional DLLs. One is their limited phase capture range, and the other is restricted Voltage-Controlled Delay Line (VCDL) range to avoid false-lock to harmonics. Thus in this chapter, a new DLL-based approach for multi-phase clock generation is presented. The proposed ADMCG uses a TDC to choose a reasonable delay range rather than to use self-correcting circuit. Thus its operation is very robust and can avoid possible false-lock as in conventional designs. The lock-in time of the proposed ADMCG can also be reduced by adding TDC module. After TDC operation, a fixed step search scheme is used in the ADMCG to fine-tune the output phase accuracy.

In chapter 6, an automated synthesis design methodology for ADPLL/ADDLL /ADMCG is presented. In SoC design, the design time for each module is restricted. Thus each module should better be a reusable design so that the total design time for the SoC can be reduced. However, for different applications, the ADPLL/ADDLL/ADMCG may have different operating ranges or different lock-in time requirements, making it hard to design one ADPLL/ADDLL/ADMCG suitable for all applications. As a result, it often needs to redesign the ADPLL/ADDLL/ADMCG for target application and design phase becomes longer. Thus in this chapter, a proposed automated synthesis methodology uses both benefits of digital VLSI and cell-based design to build up user-specified ADPLL/ADDLL/ADMCG in a short time, making it very suitable for System-On-Chip (SoC) designs.

In chapter 7, we make conclusions and describe several design issues needed to be further explored in the near future.

# **Chapter 2**

# Timing Critical Modules in ADPLL and ADDLL Architecture

In this chapter, the design for delay cells and phase detectors are presented. They are the important modules in ADPLL/ADDLL design. The resolution of the delay cells and the sensitivity of the phase detector have large influences on the jitter performance of the output clock. They also have large effects on the final frequency error or phase error. As a result, they need to be designed carefully. And since we want to propose a cell-based ADPLL/ADDLL design, how to overcome the limitations of the standard cells to build up a high resolution delay cell and high sensitivity phase detector are the important design challenges for our research.

The delay cells are used to construct a ring oscillator and produce the desired output frequency in ADPLL design. In ADDLL design, delay cells are used to build a delay line and outputs the delayed version of the input clock. The delay cell must be easy to adjust its delay time, and the resolution of the delay cell should be sufficient enough to meet the requirements for the output clock.

The phase detector is used in ADPLL/ADDLL design to detect the phase error between

the reference clock and output clock. The phase detector's dead zone may cause the wrong operations in phase acquisition process. Thus how to reduce the dead zone of the phase detector is very important to improve the stability for the ADPLL/ADDLL and also minimize the static phase error.

The organization of this chapter is as follows. In section 2.1, the proposed high resolution delay cell is presented. And how to use the standard cells to build up this delay cells is also explained in this section. In section 2.2, the proposed high sensitivity phase and frequency detector (PFD) is presented. The proposed PFD is also constructed by standard cells. Finally, a brief summary is made in section 2.3.

### 2.1 Design of High Resolution Delay Cells

In analog delay cells, the delay cell is controlled by control voltage/current, and the output delay time is continuous over the controllable range. But in digital-controlled delay cell, the output delay time is quantized. And the resolution of the output delay time must be sufficient enough to meet the design specifications.

When two nearby digital control codes are applied to the delay cell, the output delay time difference is defined as the resolution of the delay cell. If an inverter-based (or buffer-based) delay line is used in delay cell design, since in this architecture, the delay cell produces different propagation delays by selecting different number of inverters (or buffers). Then the resolution of the delay cell is limited by the delay time of one inverter (or one buffer). And this resolution is often not sufficient to be used in ADPLL/ADDLL design.

Thus in previous designs, the phase blender is proposed in [19] to provide a better resolution by phase interpolation. And the delay matrix, which uses parallel tri-state buffers to enhance the resolution of the delay cell, is proposed in [8]. However, the intrinsic delay time of the phase blender is too large to be used in high-speed applications. This is because that in phase blender architecture, high resolution means the increasing of phase blender stages. And the area cost and the power consumption for the delay matrix is too large to be used in a low cost and low power design.

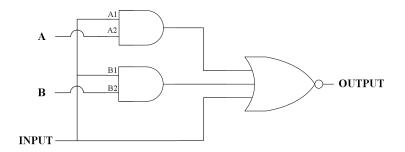

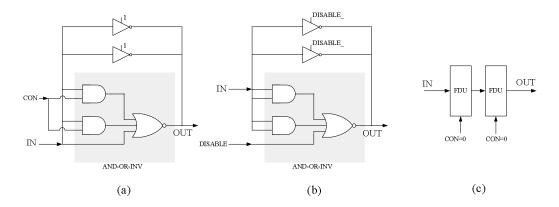

In this section, a low cost and high resolution delay cell is presented. The schematic of the proposed delay cell is shown in Fig 2.1. The function of this delay cell acts as an inverter regardless of (A, B) input value. And the value of (A, B) determines the delay time of the proposed delay cell.

Fig. 2.1: The schematic of the proposed delay cell.

The CMOS circuit realization of the proposed delay cell is shown in Fig. 2.2.

Fig. 2.2: The CMOS circuit of the proposed delay cell.

$\sim$  8  $\sim$

The delay time when the input changes from 0 to 1 and the output changes from 1 to 0 is defined as  $T_{PHL}$ . Oppositely, the delay time when the input changes from 1 to 0 and the output changes from 0 to 1 is defined as  $T_{PLH}$ .

In Fig. 2.2, when (A, B) is equal to (1, 1), the  $T_{PHL}$  of the delay cell is always smaller than the cases: (A, B) = (0, 1) or (1, 0). And when (A, B) = (1, 0) or (0, 1), the  $T_{PHL}$  of the delay cell is always smaller than the case: (A, B) = (0, 0). This is because the change of (A, B) value determines that how many pull-down paths will be turned on/off. So the resolution enhancement can be achieved by using the proposed delay cell.

Fig. 2.3: The proposed high resolution delay cell.

In Fig. 2.1, this delay cell is named as an AOI (AND-OR-INVERSE) type delay cell, and it is a basic cell and can be found in standard cell library. The control signals can be used to adjust the  $T_{PHL}$  of the AOI type delay cell. Oppositely, the OAI (OR-AND-INVERSE) type cell can be controlled to adjust the  $T_{PLH}$  of the delay cell.

If those two type delay cells are cascaded, the resolution of the delay cell can be further enhanced. Fig. 2.3 shows the proposed high resolution delay cell, and it can be used to perform fine-tuning in ADPLL/ADDLL design. Both AOI type delay cell and OAI type delay cell are shunted with two tri-state buffers. And shunted tri-state buffers are used to increase

~ 9 ~

the controllable range of the proposed high resolution delay cell.

In the proposed high resolution delay cell, in total six bits: (EN1, A1, B1, EN2, A2, B2) can be used to control the delay cell. Thus, in total 64 ( $=2^{6}$ ) different delays can be provided. To design the proposed delay cell, first, the suitable standard cells must be selected from the cell library. And the SPICE circuit simulation for the proposed delay cell must be performed to measure the delay time ( $T_{PHL}$  and  $T_{PLH}$ ) of the delay cell for all possible 64 cases. After SPICE simulation, the lookup table for mapping the binary control code versus delay cell control code can be created.

| 111                 |         | $(\mathbf{I} \mathbf{b}), \mathbf{COD}$ |         |                                    |         |                                    |         |

|---------------------|---------|-----------------------------------------|---------|------------------------------------|---------|------------------------------------|---------|

| $T_{PHL} + T_{PLH}$ | CODE    | T <sub>PHL</sub> +T <sub>PLH</sub>      | CODE    | T <sub>PHL</sub> +T <sub>PLH</sub> | CODE    | T <sub>PHL</sub> +T <sub>PLH</sub> | CODE    |

| 0802.7026           | 000 011 | 0674.2368                               | 000 100 | 0622.3394                          | 010 111 | 0580.2200                          | 111 001 |

| 0777.6740           | 000 010 | 0672.7012                               | 001 111 | 0622.0947                          | 101 001 | 0578.2402                          | 110 000 |

| 0759.8178           | 000 001 | 0670.2695                               | 100 010 | 0620.1069                          | 011 111 | 0577.0692                          | 100 101 |

| 0759.3041           | 001 011 | 0667.4821                               | 101 011 | 0613.8635                          | 101 000 | 0572.2359                          | 111 000 |

| 0751.3155           | 000 000 | 0666.1494                               | 010 001 | 0611.3577                          | 100 111 | 0568.2607                          | 100 100 |

| 0736.0601           | 001 010 | 0663.9600                               | 011 001 | 0605.6821                          | 110 010 | 0563.3331                          | 101 110 |

| 0718.9363           | 001 001 | 0658.9083                               | 010 000 | 0604.3907                          | 010 110 | 0549.1761                          | 110 111 |

| 0714.0263           | 000 111 | 0657.2062                               | 011 000 | 0602.3159                          | 011 110 | 0549.1071                          | 101 101 |

| 0711.8740           | 001 000 | 0655.3770                               | 001 110 | 0599.4157                          | 111 010 | 0543.4591                          | 111 111 |

| 0707.5820           | 010 011 | 0650.9609                               | 100 001 | 0591.4753                          | 100 110 | 0540.5546                          | 101 100 |

| 0704.4837           | 011 011 | 0642.2144                               | 001 101 | 0591.0464                          | 010 101 | 0529.1033                          | 110 110 |

| 0697.3336           | 100 011 | 0642.0410                               | 100 000 | 0589.1943                          | 011 101 | 0523.2402                          | 111 110 |

| 0695.9196           | 000 110 | 0641.0289                               | 101 010 | 0586.3467                          | 110 001 | 0514.6414                          | 110 101 |

| 0683.6460           | 010 010 | 0634.8068                               | 001 100 | 0583.3829                          | 010 100 | 0508.8459                          | 111 101 |

| 0682.2107           | 000 101 | 0632.4963                               | 110 011 | 0583.0358                          | 101 111 | 0506.1100                          | 110 100 |

| 0681.0558           | 011 010 | 0626.2559                               | 111 011 | 0581.7245                          | 011 100 | 0500.2978                          | 111 100 |

Table 2.1: CONTROL CODE VS. DELAY TIME OF THE PROPOSED DELAY CELL TIME UNIT: (PS), CODE: (EN1 A1 B1 EN2 A2 B2)

Table 2.1 lists the simulated delay time of the proposed high resolution delay cell versus delay cell control codes. In this simulation, a standard 0.35µm 1P4M CMOS process cell library is used to construct the delay cell.

If the proposed delay cell is applied to be the fine-tuning stage of the DCO. Then the value of  $(T_{PHL}+T_{PLH})$  means the change of the output clock period. The resolution of the DCO can be improved to the resolution of the proposed delay cell. And in this simulation, the average resolution of the proposed delay cell is about 5ps = ((802.7026 ps - 500.2978 ps)/64).

Since in the proposed delay cell, there only six standard cells are used. Thus its area cost and power consumption is very low, and its resolution is also sufficient to be used in ADPLL/ADDLL design.

### 2.2 High Sensitivity Phase and Frequency Detector Deign

The phase detector (PD) can detect the phase error between the reference clock and the output clock. And it generates the up or down pulse to control the ADPLL/ADDLL. In analog phase-locked loop or analog delay-locked loop, the pulse width of the up/down pulse, which means the amount of the phase error, controls the charge/discharge time for the charge pump capacitor. However, in ADPLL and ADDLL, only the polarity information (i.e. lead or lag) is taken from the phase detector, and thus the pulse width information is not used. This is because the ADPLL/ADDLL controller is a cycle-based finite state machine. Thus it is not possible to use the pulse width information for the ADPLL/ADDLL controller unless some circuits likes the time-to-digital converter (TDC) is used [39].

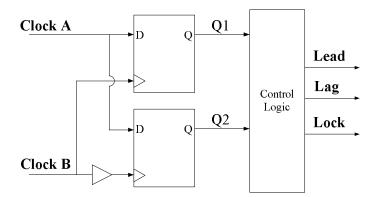

Fig. 2.4: The sample-based phase detector.

Since the phase detector used in ADPLL/ADPLL design only needs to detect the polarity information. The sample-based phase detector is often used as in previous designs [18]. In

those phase detectors, they determine lead/lag information by using output clock as the sampling clock to sample the reference clock.

The sample-based phase detector is shown in Fig. 2.4. Clock B is output clock and clock A is the reference clock. Both clock B and its delayed one create a sampling window for detecting the transition of clock A. If the sampling values (Q1, Q2) are different, the transition of the clock A is detected. And then the control logic can use the sampled values to generate the lead or lag information for the ADPLL/ADDLL controller.

But when the reference clock edge (clock A) is very close to the output clock edge (clock B), the phase detector may produce wrong lead/lag information for the ADPLL/ADDLL controller. The minimum phase error, which can be detected by the phase detector, is called the dead zone of the phase detector. If standard cells are used to construct the phase detector, the resulting dead zone is often too large to be used in ADPLL/ADDLL design. The limitations of this type phase detector often comes from the timing requirements (such as: setup time and hold time) for the D-Flip/Flop.

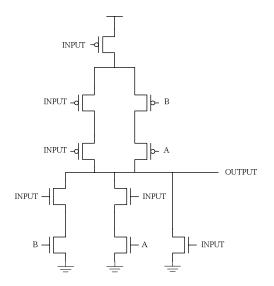

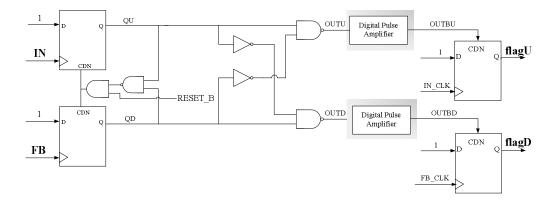

Fig. 2.5: The proposed high sensitivity phase and frequency detector.

To overcome the disadvantages and limitations of the traditional sample-based phase detector, a new phase and frequency detector (PFD) is presented. Fig. 2.5 shows the

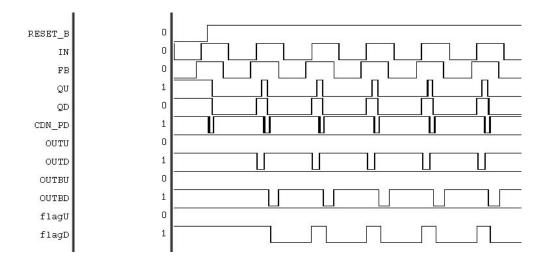

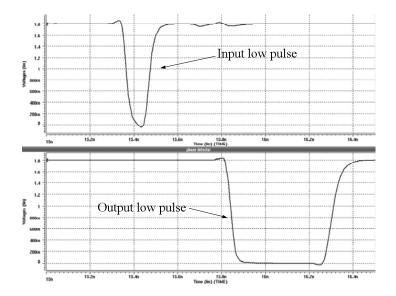

schematic of the proposed high sensitivity PFD. The proposed PFD consists of one three-state phase detector and two digital pulse amplifiers. The simulation waveform of the proposed high sensitivity PFD is shown in Fig. 2.6. When output clock (FB) leads reference clock (IN), flagD produces a low pulse and flagU remains at high. Oppositely, when output clock (FB) lags reference clock (IN), flagU produces a low pulse and flagD remains at high. And those flagU and flagD signals are used to control the operation of the ADPLL/ADDLL controller.

Fig. 2.6: The simulation waveform of the proposed PFD.

In Fig. 2.5, when the output clock (FB) is very close to the reference clock (IN), the pulse width of three-state phase detector's output (i.e. OUTU or OUTD) becomes very small. This narrow low pulse (OUTU or OUTD) can not correctly clear the D-Flip/Flop's output (flagU or flagD). Thus the dead zone of the proposed PFD is limited by this minimum pulse width requirement for the D-Flip/Flop's clear pin (CDN). This timing requirement is often about several hundred pS in typical standard cell library.

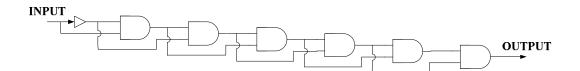

To improve the sensitivity of the proposed PFD, two digital pulse amplifiers are connected at the output of three-state phase detector (i.e. OUTU or OUTD). The schematic of the digital pulse amplifier is shown in Fig. 2.7. It uses the cascaded two-input ANDs architecture to increase the low pulse width of OUTU and OUTD. The output pulses are named as OUTBU and OUTBD. The digital pulse amplifier enlarges the phase error between reference clock (IN) and output clock (FB), thus the following D-Flip/Flops can detect it.

Fig. 2.7: The digital pulse amplifier.

Fig. 2.8: The SPICE simulation waveform of the digital pulse amplifier.

Fig. 2.8 shows the SPICE circuit simulation waveform of the digital pulse amplifier. The input is delayed and is "AND" with itself, thus the pulse width of the low pulse is extended. Ideally, increasing the number of "AND" stages can increase the sensitivity of the proposed PFD. But when the phase error between reference clock and output clock becomes very small, the low pulse at OUTU and OUTD may be disappeared or may be not full swing voltage. In this case, the digital amplifier becomes useless. So the real sensitivity of the proposed PFD

can be determined after SPICE simulation.

In the simulation which is shown in Fig. 2.8, a standard 0.18 $\mu$ m 1P6M CMOS process cell library is used to construct the proposed high sensitivity PFD. From SPICE simulation, the input low signal whose pulse width is larger than 20ps will be increased to more than 600ps to meet the minimum pulse width requirement of the D-Flip/Flop's clear pin. As a result, the sensitivity of the proposed PFD can be improved to  $\pm$ 20ps, and this high sensitivity ability is very suitable to be used in ADPLL/ADDLL design.

Besides detecting the phase error, the proposed PFD also has the ability to detect the frequency difference between reference clock and output clock. Both flagU and flagD will be clear to high after the next rising edge of reference clock and output clock occurs respectively. Thus if the frequency of the output clock is higher than reference clock, the flagD will have more numbers of low pulse than flagU, and this will cause the ADPLL controller to slow down the DCO's output frequency. So the proposed PFD is also suitable to be used in ADPLL design to detect frequency error.

### 2.3 Summary

In this chapter, the timing critical modules for ADPLL and ADDLL are presented. The proposed delay cell architecture overcomes the limitations of using the standard cells to construct the high resolution delay cell, and it also has lower cost and lower power consumption than the traditional designs. Thus it is very suitable to be used in ADPLL and ADDLL. The proposed high sensitivity PFD is also presented in this chapter. The proposed PFD uses the digital pulse amplifier to improve the sensitivity of the traditional three-state phase and frequency detector, and thus it is also very suitable to be used in the ADPLL and ADDLL design.

# **Chapter 3**

# **All-Digital Phase-Locked Loop Design**

In this chapter, the design for all-digital phase-locked loop (ADPLL) is presented. The phase-locked loops (PLL) are widely used for many communication applications, such as frequency synthesizer, clock multiplier, clock and data recovery circuit, or input clock jitter filtering. It had become an essential function block for current System-On-Chip (SoC) design. And how to design the PLL in a more efficient way is a very important design issue for chip makers.

Due to high integration of VLSI system, PLL often operates in a very noisy environment. The jitter less than  $\pm 4\%$  of the clock cycle time is typically needed to avoid functional failures in a microprocessor [1]. However, the digital switching noise coupled through power supply and substrate induces considerable noise into noise-sensitive analog circuits [1,3-7].

Traditionally, many analog approaches are proposed to improve the jitter performance of PLL, such as: choosing a narrow bandwidth or using a low gain Voltage-Controlled Oscillator (VCO) [3]. However, those analog approaches often result in long lock-in time and increasing design complexity of PLL.

In recently years, ADPLL became more attractive since they yield better testability, programmability, stability and portability over different processes [8,9]. And they can reduce

$\sim$  16  $\sim$

the system turn around time. But the jitter performance and the frequency resolution of the traditional ADPLLs are not as well as analog PLLs. This is because it is difficult to design the high resolution digital-controlled oscillator (DCO) and high sensitivity phase and frequency detector (PFD).

However, the ADPLL has the ability to achieve fast-locking in a short period, and it is very suitable for fast-locking applications. If the jitter performance of the ADPLL can be improved, then the ADPLL can be used in more applications. Thus how to design a fast-locking ADPLL with low-jitter performance in a short design time is the goal for this research.

In this chapter, an ADPLL using the proposed high resolution delay cell and the proposed high sensitivity PFD is presented. The design for the delay cell and the PFD was already discussed in chapter 2. The proposed delay cell can reduce both cost and design time for building a high resolution cell-based DCO. And the proposed PFD can improve the jitter performance and reduce the frequency error for the output clock. Moreover the flexible ADPLL architectures for different target applications are presented in this chapter for a truly portable and cost-effective ADPLL-based frequency synthesizer solution.

The organization of this chapter is as follows. In section 3.1, the overview of PLL is discussed. In section 3.2, the design trade-off between different PLL architectures is discussed. In section 3.3, the proposed ADPLL architecture is presented. In section 3.4, the test chip which implements of the proposed ADPLL using standard 0.35µm CMOS process is presented. In section 3.5, the simulation and measurement results of the test chip are presented. Finally, a brief summary is made in section 3.6.

### **3.1 Overview of Phase-Locked Loop (PLL)**

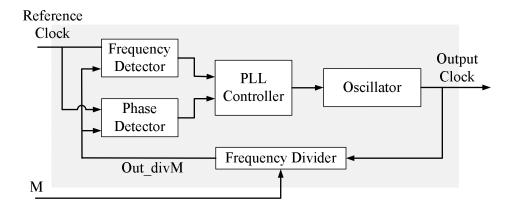

The general PLL architecture is shown in Fig. 3.1. The input of PLL is reference clock

and programmable divide ratio M, and output clock outputs from the internal oscillator. The PLL keeps tracking the frequency and the phase of reference clock, and it speeds up or slows down the internal oscillator to minimize frequency and phase error between divided output clock (Out\_divM) and reference clock. After PLL is locked, the frequency of output clock is M times higher than reference clock, and the phase of output clock is synchronized with reference clock.

Fig. 3.1: The general PLL architecture.

The PLL lock-in process is separated into frequency acquisition and phase acquisition. The frequency detector detects the frequency difference between reference clock (Reference Clock) and divided output clock (Out\_divM). And the PLL controller controls the internal oscillator's output frequency to minimize frequency error. Thus high resolution oscillator is needed to generate accurate frequency output. After frequency acquisition is completed, the PLL turns into phase acquisition and phase maintaining mode.

The lock-in time of PLL is mainly determined by the frequency acquisition time, thus how to reduce frequency acquisition time is very important to a fast-locking PLL design. In previous designs, the adaptive gain control PLL [2,37] or the TDC-based ADPLL [39] are proposed to speed up the frequency acquisition process.

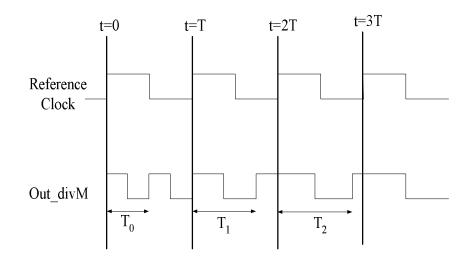

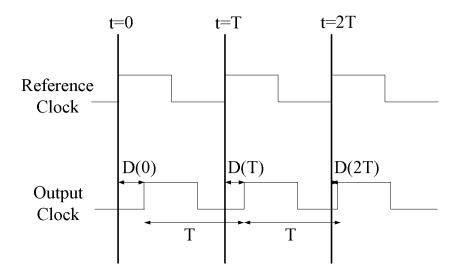

Fig. 3.2: The frequency acquisition process of PLL.

Fig. 3.2 illustrates the frequency acquisition process of PLL. If we assume the oscillator is reset to high at every rising edge of Reference Clock, and the output period of Out\_divM is F(t), where t is time. And we assume at time=0, the frequency detector finds that output frequency of oscillator is higher than Reference Clock. The PLL controller will control the internal oscillator to slow down.

If step size for frequency acquisition is F\_STEP, then the output period of Out\_divM at t=T becomes  $F(T)=T_0 + F_STEP$ , and the output period of Out\_divM at t=2T becomes  $F(2T)=T_1 + F_STEP = T_0 + 2*F_STEP$ . The general form to determine the output period of Out\_divM at time t can be expressed as Eq. 3.1.

$$F(nT) = F((n-1)T) - F\_STEP, \text{ if } F((n-1)T) > T,$$

$$F((n-1)T) + F\_STEP, \text{ if } F((n-1)T) < T$$

$$F((n-1)T), \text{ if } F((n-1)T) = T \qquad (Eq. 3.1)$$

When F(t) becomes T or the frequency detector can not distinguish the frequency difference between Reference Clock and Out\_divM, the frequency acquisition is done.

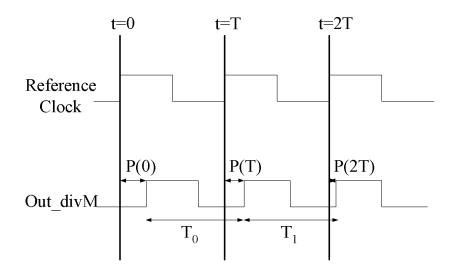

After frequency acquisition is completed, the PLL starts to trace the phase of reference clock. Fig. 3.3 illustrates the phase acquisition process of PLL. If we assume the frequency

$\sim$  19  $\sim$

error between Reference Clock and Out\_divM is zero after frequency acquisition, and the phase error between Reference Clock and Out\_divM is P(t), where t is time. The initial phase error is P(0). And we assume at time=0, the phase detector finds that Out\_divM lags behind Reference Clock. The PLL controller will control the internal oscillator to speed up.

If step size for phase acquisition is P\_STEP, then the phase error at t=T becomes  $P(T) = P(0) + T_0 - T = P(0) - P_STEP$ . And the phase error at t=2T is  $P(2T) = P(T) + T_1 - T = P(0) - P_STEP - 2*P_STEP$ . The general form of phase error at time t can be expressed as Eq. 3.2.

$$P(nT) = P(0) - \sum_{n} n * P \_STEP$$

(Eq. 3.2)

where we assume that the Out\_divM still lags behind the Reference Clock after several updates of the oscillator frequency. When P(t) becomes negative or zero, the phase acquisition process is completed.

Fig. 3.3: The phase acquisition process of PLL.

After phase error is eliminated, phase acquisition process is completed. PLL controller will restore oscillator's frequency back to the baseline frequency which is determined by frequency acquisition process, and the PLL turns into phase maintaining mode. In this phase maintaining mode, the PLL keeps tracking the phase of reference clock by fine-tuning oscillator's output frequency.

In phase acquisition process, phase detector must provide correct phase relationship information about reference clock and divided output clock. The dead zone of phase detector will increase phase acquisition time and final phase error. Thus how to design a high sensitivity phase detector is a design challenge for PLL design. Since the operating range and output frequency accuracy is determined by the internal oscillator, the design for high resolution oscillator is also an important design challenge for PLL design.

### **3.2 Design Trade-Off in Different PLL Architectures**

PLL design is a trade-off among jitter performance, lock-in time, area cost power consumption, circuit complexity and design time. Thus it is hard to design one PLL suitable for all applications. For fast-locking frequency synthesizer applications, such as a frequency hopping multiple access systems, the lock-in time is the most critical design issue. And for portable or mobile applications, lock-in time is also very important since the PLL must support fast entry and exit from power management techniques [9].

In traditional analog PLL designs, fast acquisition requires tuning of the Voltage-Controlled Oscillator (VCO) free-running frequency near the desired frequency in advance or to increase loop bandwidth. But increasing the loop bandwidth degrades jitter performance, and the exact VCO tuning range is not easy to be achieved since there always has process variations, voltage variations, and temperature variations (PVT variations).

Thus a Digital Frequency-Difference Detector (DFDD) is proposed in [2] to convert the frequency difference directly to the digital value, and then change the gain for VCO control adaptively. The dual-loops PLL architecture [37] uses one loop for fast tracking the suitable frequency range and the other loop fine-tuning the output. Both of them proposed a concept

that for fast lock-in time, the VCO gain or the loop bandwidth should be increased during the frequency acquisition process. And after frequency is locked, it should return to its normal value to preserve the low jitter performance. But the circuit complexity is increased due to this adaptive gain control ability.

A different way to achieve fast lock-in time is proposed in [38]. It uses a digital hybrid PLL (DH-PLL) with Digital Look-up Table (DLT) to shorten settling time and achieve fast switching speed at every frequency synthesis. This design uses a DLT to directly adjust VCO output to the desired frequency, and then uses a traditional analog PLL to fine-tune the output. However, this digital look-up table is still dependent on PVT variations. As a result, acquisition time increases in proportion to the initial frequency difference.

From the previous PLL architectures [2,37,38], the methods for fast-locking PLL design can be classified into two types: one uses an adaptive gain control for the frequency acquisition process, and the other uses a look-up table to speed up the frequency acquisition process.

To further speed up the lock-in time, an all-digital phase-locked loop (ADPLL), which uses a Time-to-Digital Converter (TDC) circuit to quantize the reference clock period into multiples of inverter delay times, is proposed in [39]. This PLL replaces the DLT [38] by TDC to against PVT variations and speeds up the frequency acquisition process. Since the TDC and the DCO are suffered from the same PVT variations, the TDC measured value is more accurately than the DLT [38], and the lock-in time of the PLL can be further reduced. But the area cost for the TDC digital processing unit is a problem if a small chip area is required.

For clock multiplier applications, the phase error between reference clock and output clock is very important. Since the ring oscillator has jitter accumulation problem, it is not easy to minimize the phase error. In ADPLL [9], the anchor register is used to store the baseline frequency, thus the ADPLL controller can keep tracking the phase of the reference clock. But the phase error of the PLL-based clock multiplier may become worst when the input jitter from the reference clock exists or the multiplication ratio is increased.

The DLL-based clock multiplier [40-42], which generates the output clock from the delayed version of reference clock, can efficiently reduce the phase error. But it is not suitable for a programmable design since the multi-phase delay line is not a scalable design. So the PLL-based clock multiplier is still more flexible than the DLL-based clock multiplier.

The Digital Controlled PLL (DCPLL) [2] has been proposed to achieve fast lock-in time. But due to low sensitivity of frequency detector and resolution limitation of D/A converter, its jitter performance is worse than analog designs. An ADPLL proposed in [9] can achieve fine resolution and fast lock-in time. However its DCO needs to be full-custom designed, making it difficult for porting to different processes as design requests. A complete cell-based ADPLL is proposed in [8], where fine-search delay matrix architecture is developed to improve DCO's resolution. Also two DCOs are exploited to reduce output clock jitter effectively. However the proposed fine-search delay matrix occupies large silicon area and has high power consumption.

From the above discussions, a better ADPLL architecture should be easily modified to fit different applications. Thus in the next section, a flexible ADPLL architecture is proposed for most applications. The proposed ADPLL architecture takes the advantages of the TDC-based ADPLL [39] and the portability of the cell-based ADPLL [8] to build up a low-jitter, low-cost, fast-locking and cell-based ADPLL.

### **3.3 The proposed ADPLL Architecture**

### 3.3.1 ADPLL Architecture Overview

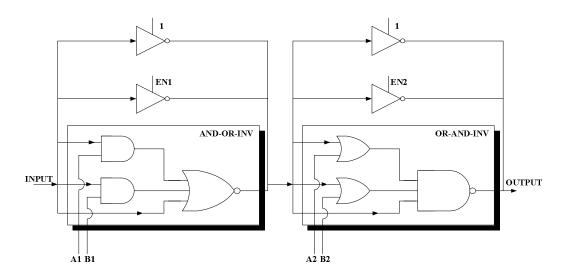

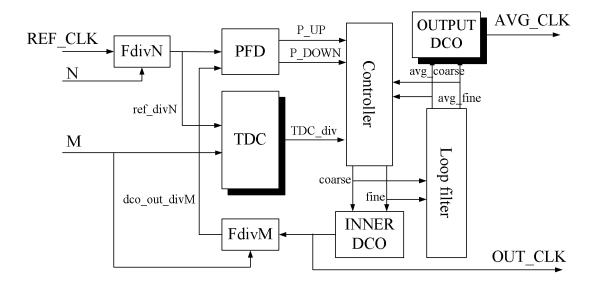

Fig. 3.4: The proposed ADPLL architecture.

The proposed ADPLL architecture is shown in Fig. 3.4. The ADPLL consists of Phase and Frequency Detector (PFD), Time-to-Digital Converter (TDC), ADPLL Controller, INNER DCO, OUTPUT DCO, loop filter, input frequency divider (FdivN) and feedback frequency divider (FdivM). M and N inputs are used for programming frequency divider and input divider respectively.

The PFD detects the frequency difference and phase error between divided reference clock (ref\_divN) and divided INNER DCO's output clock (dco\_out\_divM), and it outputs up (P\_UP) and down (P\_DOWN) signal to indicate that the INNER DCO should speed up or slow down respectively. The ADPLL controller takes those control signals from the PFD and performs update of the DCO control code (coarse, fine). This DCO control code is also sent to the loop filter. After ADPLL is locked, the DCO control code is converged to the fine-tuning range. And then both frequency acquisition and phase acquisition are achieved.

The loop filter takes DCO control code from the ADPLL controller, and it detects the variations range of the DCO control code after ADPLL is locked, and outputs average control code (avg\_coarse, avg\_fine) for OUTPUT DCO. After ADPLL is locked, every time

$\sim$  24  $\sim$

when the PFD's output changes from up to down or vice versa, the ADPLL controller restores this average DCO control code from the loop filter for phase acquisition and phase maintaining.

In the proposed ADPLL architecture, the TDC is an optional module and is only used for fast-locking ADPLL. If the lock-in time is not a critical design issue or a smaller chip area is required, this module is removed from the architecture, and then the binary search ADPLL controller is used for frequency acquisition.

For frequency synthesis application, the loop filter can filter out DCO control code variations and controls OUTPUT DCO to provide a low-jitter clock output (AVG\_CLK). For clock multiplier applications, OUTPUT DCO is removed from the architecture, and in-phase output clock directly outputs from the OUT\_CLK.

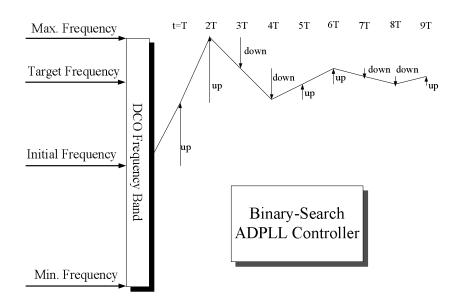

#### **3.3.2 Design for Binary Search ADPLL Controller**

In binary search ADPLL controller, a binary search scheme is used when it searches for the target frequency. Fig 3.5 illustrates the frequency acquisition process. The frequency acquisition starts from middle frequency band of the DCO. If DCO can provide "n" different frequencies, the search step is "n/4" in the initial state. When output frequency is lower than target frequency, ADPLL controller adds current search step to DCO control code, and this increases the output frequency of DCO. Oppositely, when output frequency is higher than target frequency, ADPLL controller subtracts the DCO control code to lower the output frequency of DCO.

Whenever the PFD's output changes from up (P\_UP) to down (P\_DOWN) or vice versa, the search step is divided by 2. And after the search step reduces to 1 (i.e. one fine-tuning step of the INNER DCO), the frequency acquisition is done. Then the ADPLL controller enters phase acquisition and phase maintaining mode. In this mode, the ADPLL controller adjusts the fine-tuning control code of the INNER DCO to eliminate the phase error between divided reference clock (ref\_divN) and divided INNER DCO's output clock (dco\_out\_divM) whenever it receives the up (P\_UP) or down (P\_DOWN) from PFD.

Fig. 3.5: The Binary search ADPLL controller.

The ADPLL's closed-loop response time is determined by the response time of DCO, delay time of ADPLL controller and frequency divider. Therefore DCO's control code can only be updated at every "m" cycles, instead of every reference clock cycle. Here "m" is determined by closed-loop's response time. In Fig. 3.5, it shows that the update period (T) for DCO control code is "m" reference clock cycles. Hence, the worst-case lock-in time for this frequency acquisition algorithm, in term of reference clock cycles can be express as Eq. 3.3.

$$T(n) = m^{*}(1 + 2^{*}\log_{2}(n/2)) = m^{*}(2^{*}\log_{2}(n) - 1)$$

(Eq. 3.3)

### 3.3.3 Design for TDC-Based Fast-Locking ADPLL Controller

For fast-locking applications, lock-in time is the most critical design issue. Thus in the

proposed architecture, TDC is used to quickly calculate the nearest control code for DCO to produce the desired frequency. TDC can convert the reference clock's period information to multiples of delay cell's delay time. Hence, ADPLL controller can use this information to quickly jump to the desired frequency band. And then ADPLL performs fine-tuning to reduce the residual frequency error and phase error. As a result, the lock-in time can be reduced by adding TDC module.

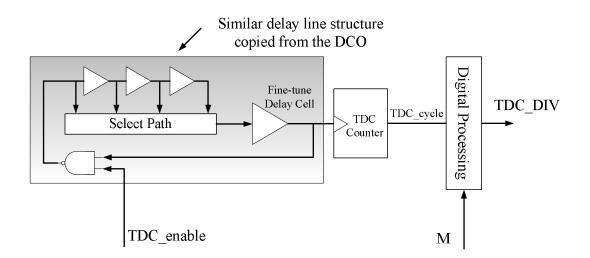

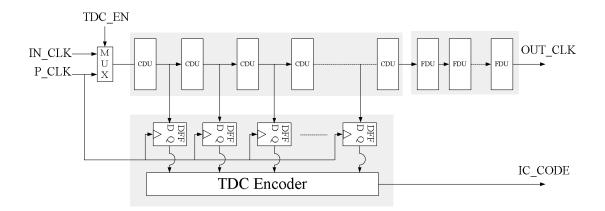

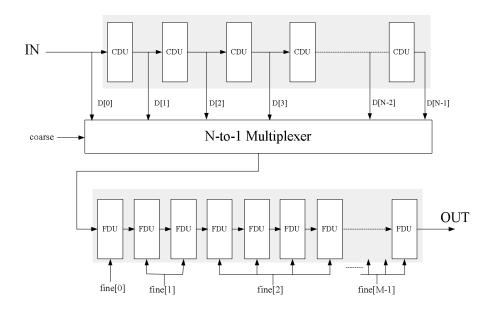

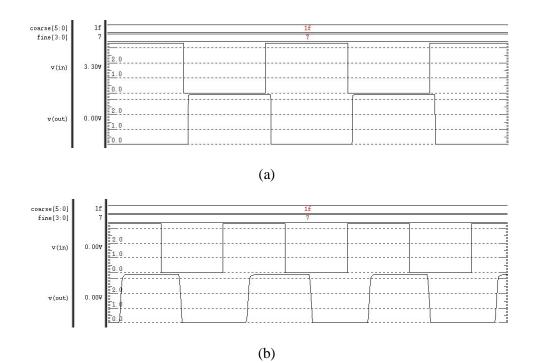

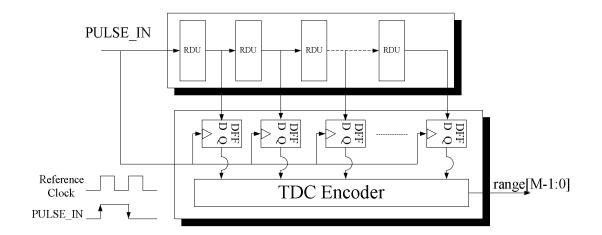

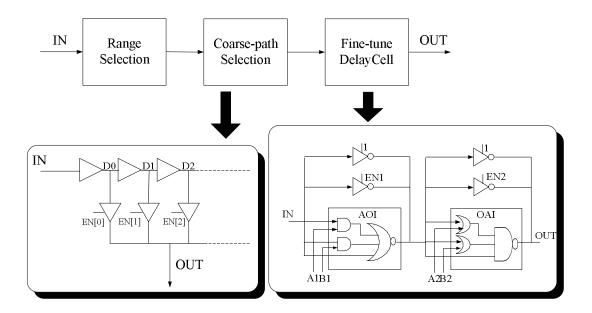

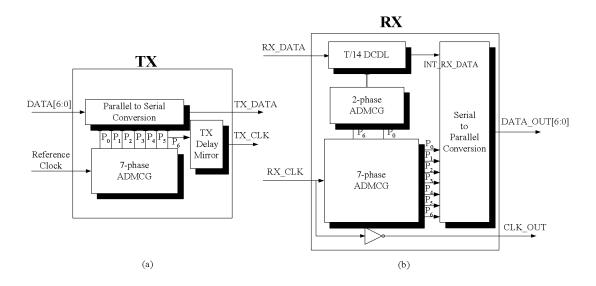

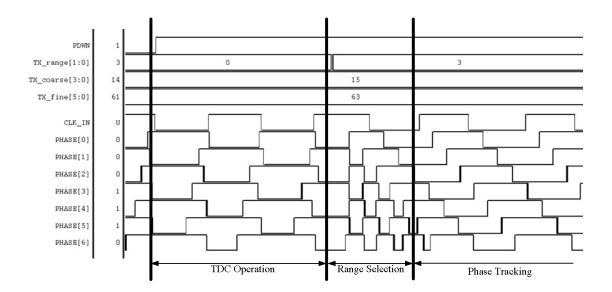

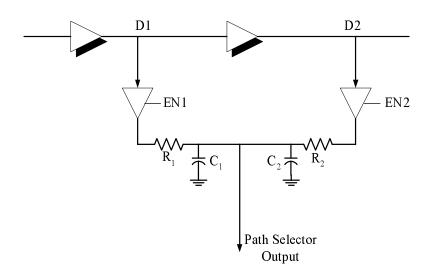

Fig. 3.6 shows the architecture of the proposed TDC for fast-locking ADPLL. To make sure that the TDC measured value can be directly applied to DCO, the ring delay line of TDC has a copied structure from the DCO with some reductions, and the difference is that only three coarse-tuning delay cells are used in TDC path selector. The detail DCO structure is discussed in section 3.4.1.

After system reset and with the first rising edge of reference clock, TDC is turned on (TDC\_enable=1), and ring delay line of the TDC begins to oscillate. Output clock of the ring delay line triggers TDC counter to count up until the second rising edge of reference clock comes. Then TDC is turned off (TDC\_enable=0).

Fig. 3.6: The structure of the proposed TDC for fast-locking ADPLL

The TDC counted value: TDC\_cycle means that the reference clock's period can be quantized as the multiples of  $T_{TDC-ring}$ , where  $T_{TDC-ring}$  means the oscillation period of the TDC ring delay line. The value of  $T_{TDC-ring}$  can be expressed as Eq. 3.4.

$$T_{\text{TDC-ring}} = 3*\text{COARSE}_{\text{UNIT}} + T_{\text{select-path}} + T_{\text{Fine-tune}} + T_{\text{RESET}}$$

(Eq. 3.4)

where  $T_{select-path}$  is delay time of path selector and  $T_{Fine-tune}$  is the delay time of fine-tuning delay cell, and  $T_{RESET}$  is the delay time for reset stage.

If n coarse-tuning delay cells are needed in DCO's coarse-tuning delay stage to produce the desired output frequency, output clock period of the DCO can be express as Eq. 3.5.

$$T_{DCO} = n*COARSE\_UNIT + T_{select-path} + T_{Fine-tune} + T_{RESET}$$

(Eq. 3.5)

If we let  $T_Z = T_{select-path} + T_{Fine-tune} + T_{RESET}$ , and the desired output frequency should be M/N times of the reference clock frequency, and Eq. 3.6 must be satisfied.

$$M*T_{DCO} = T_{TDC-ring}*(TDC_cycle/N)$$

$=> M*N*(n*COARSE_UNIT + T_Z) = (3*COARSE_UNIT + T_Z) * TDC_cycle$

$$=> n= 3*(TDC_cycle/M*N) + (T_Z/COARSE_UNIT)*((TDC_cycle-1)/M*N)$$

(Eq. 3.6)

To reduce the circuit complexity for TDC, TDC\_cycle-1 is reduced to TDC\_cycle, and since  $T_Z$  contains five gate delays,  $T_Z$ /COARSE\_UNIT is replaced by 5. Therefore the equation can be further reduced and expressed as Eq. 3.7.

$$n \cong 8 \text{TDC_cycle/(M*N)}$$

(Eq. 3.7)

Thus digital processing unit takes the counted value (TDC\_cycle) from TDC counter and performs the calculation of Eq. 3.7, and then outputs the DCO control code (TDC\_DIV) to ADPLL controller. The ADPLL controller takes this value as the initial DCO control code. After that, it fine-tunes the output by up (P\_UP) and down (P\_DOWN) control signals from PFD.

The bit width of TDC counter and TDC digital processing unit are determined by the maximum reference clock period (i.e the lowest reference clock rate). After user specifies the

$\sim$  28  $\sim$

reference clock range, the bit width must be large enough to avoid overflow in TDC counter.

Since in Eq. 3.7, one divider is needed for calculation of the suitable DCO control code. Thus when TDC module is used for the ADPLL design, the area cost is increased, but the frequency acquisition time can be reduced.

The area cost for binary search ADPLL controller is much lower than TDC-based fast-locking ADPLL controller. Hence binary search ADPLL controller is very suitable for a low-cost ADPLL design and still has faster lock-in time than traditional analog PLLs. And for fast-locking applications, the TDC-based ADPLL controller is preferred.

## **3.4 The ADPLL Circuit Design**

In the proposed ADPLL architecture, all functional blocks are implemented with standard cells. Thus design time for the ADPLL is reduced by the proposed cell-based architecture. And the limitations of the cell-based design are overcome by using the proposed high resolution delay cell and high sensitivity PFD.

### 3.4.1 Design for Digital-Controlled Oscillator

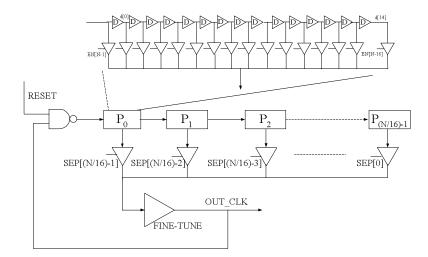

Fig. 3.7: The proposed cell-based DCO architecture.

$\sim$  29  $\sim$

The proposed cell-based DCO architecture is shown in Fig. 3.7. In the test chip, the DCO is implemented with TSMC 0.35µm 1P4M CMOS standard cell library. It is separated into two stages: coarse-tuning stage and fine-tuning stage.

In coarse-tuning stage, the coarse-tuning delay chain with 64-to-1 path selector architecture is used to provide different delays for coarse-tuning. The 64-to-1 path selector architecture is implemented with tri-state buffers. The DCO coarse-tuning encoder encodes 6 (= $\log_2(64)$ ) bits coarse-tuning control code into 64-bit one-hot path selection control signals. This architecture has advantage of minimum intrinsic delay time in path selector to improve maximum operating frequency of the DCO. And it can be easily modified to meet different specifications for different applications.

To avoid large loading capacitance appearing in the path selector's output, the path selector is partitioned into two stages. In the first stage, every sixteen coarse-tuning delay blocks will select a partial output. And the second stage path selector will select the final output. The delay time difference between two neighbor paths is determined by one coarse-tuning delay cell. The ( $T_{PHL} + T_{PLH}$ ) of one coarse-tuning delay cell is about 300ps in the target process. Thus when DCO's coarse-tuning control code increases one or decreases one, the amount of output clock's period will be changed by ±300ps.

To increase frequency resolution of the DCO, fine-tuning delay cell is added after coarse-tuning stage. The circuit of fine-tuning delay cell is show in Fig. 2.3. And the detail information about how to design the fine-tuning delay cell is discussed in section 2.1.

The controllable range of fine-tuning delay cell should cover one coarse-tuning step (i.e. 300ps). And the DCO resolution can be improved to averagely 5ps by adding fine-tuning delay cell. The maximum output frequency of DCO is 545MHz (1.833ns) and minimum output frequency of DCO is 41MHz (24.261ns) by SPICE circuit simulation.

#### **3.4.2 Design for Phase and Frequency Detector**

The circuit of cell-based PFD is shown in Fig. 2.5, and the detail information about how to design PFD is discussed in section 2.2. After using the digital pulse amplifier to increase the sensitivity of PFD, phase error up to  $\pm 50$ ps can be detected in the target process. When phase error is less than the dead zone of PFD, there will have no trigger signals sent to ADPLL controller which remains unchanged in its previous state.

#### **3.4.3 Loop Filter Design**

After ADPLL has finished frequency acquisition and phase acquisition, INNER DCO's control code becomes converged to a fine-tuning range. However the control code may have small variations due to the following factors: PFD's dead zone, DCO's finite resolution and reference clock jitter. To further improve jitter performance of the APDLL for frequency synthesizer applications, loop filter is used to filter out the resultant noise into OUTPUT DCO.

Thus the loop filter detects the maximum INNER DCO control code and minimum INNER DCO control code within 512 reference clock cycles and then outputs (DCO control code (maximum) + DCO control code (minimum)/2 as the average DCO control code for the OUTPUT DCO. As a result, the jitter performance of the output clock can be improved.

But since phase relationship between OUTPUT DCO and INPUT DCO is unknown. Thus this two DCO structure can only be used in frequency synthesizer applications, where only accurate frequency output is needed. And for phase acquisition applications, OUTPUT DCO is removed from the structure, and the output clock directly achieved from INNER DCO.

The proposed loop filter circuit is very simple. It only needs two registers and one adder. But it can greatly reduce the noise effects and reference clock jitter effects.

$\sim$  31  $\sim$

#### **3.4.4 A Systematic Approach for ADPLL Design**

A systematic way is provided to design the ADPLL with specified standard cell library. Firstly, SPICE circuit simulation of the fine-tuning delay cell should be performed to construct lookup table for mapping fine-tuning control code.

When the controllable range of fine-tuning cell is determined, a suitable coarse-tuning cell, whose delay time  $(T_{PHL}+T_{PLH})$  is less than or equal to the controllable range of fine-tuning delay cell, can be selected from cell library. And the specifications of output clock range determine the number of select paths in coarse-tuning stage.