# A Body Channel Communication Transceiver with a 16x Oversampling CDR and Convolutional Codes

Ching-Che Chung, Senior Member, IEEE, and Yi-Ting Tsai Department of Computer Science and Information Engineering National Chung Cheng University No. 168, University Rd., Min-Hsiung, Chia-Yi, Taiwan Email: wildwolf@cs.ccu.edu.tw

2022 International Symposium on VLSI Design, Automation and Test (VLSI-DAT) | 978-1-6654-0921-6/22/\$31.00 @2022 IEEE | DOI: 10.1109/VLSI-DAT54769.2022.9768085

*Abstract*—In this paper, a transceiver for human body channel (BCC) transmission is presented. BCC has the advantage of being less susceptible to interference from the external environment and consuming less power. First, the convolutional code encodes the data on the transmission side, and then the bit buffer and NRZI code are used to make the transmission more reliable, and the CRC32 code is inserted. On the receiver side, the proposed 16 times oversampling clock and data recovery (CDR) circuit recover the clock and data, and then the data are decoded by the Viterbi decoder. Finally, the correctness of the packet data is checked by the CRC32 code. The proposed BCC transceiver was implemented in TSMC 90nm CMOS process and can achieve a 5Mbps data rate with BER <  $10^{-9}$  with energy/bit 0.34nJ/b (TX) and 0.4654nJ/b (RX).

Index Terms—Body channel communication, clock, and data recovery, Transceiver, Convolutional encoder.

## I. INTRODUCTION

In wearable devices, the acquisition or transmission of biosignals is made by sensors or implantable chips. Therefore, wearable devices are becoming more popular, and the network with wearable devices and sensors is called body area network (BAN). After the body data is collected, it must be sent to the cloud server on time. Generally, the use of wireless techniques is more common. BAN using wireless techniques is called a wireless body area network (WBAN). The range of WBAN is between one and two meters. In this range, WBAN can establish a connection between sensors or wearable devices. In addition, WBAN devices must be lightweight, consume low power, and have a small size.

There are two ways to implement WBAN: One uses air transmission, such as Bluetooth and ZigBee. However, these methods have some disadvantages. The data rate of these methods is low, and these methods can be easily interfered with by other users. The other way to realize BAN uses the human body as the transmission medium is called body channel communication (BCC). BCC has relatively high energy efficiency than other methods. The power consumption of BCC is less than 10 mW; in contrast, the power consumption of Bluetooth is nearly 100 mW.

The basic idea of BCC is that two electrodes are attached to the human body. The signal is modulated and transmitted from the transmitting electrode (TX) to the receiving electrode (RX) via the human body. Then the RX restores the data of the original signal. Once the signal leaves the human body, the signal is quickly attenuated so that it can prevent eavesdropping. The BCC characteristics are studied in [1]. When the signal frequency is below 4 MHz, the impedance of the human body can be neglected because it is much lower than the impedance of the capacitive return path. Therefore, the transmission distance does not have much effect on the channel gain. However, at frequencies above 10 MHz, the air coupling capacitance between TX and RX decreases with increasing frequency, resulting in less signal loss. Then, the signal loss depends on the transmission distance [2].

Common BCC transmission methods with capacitive coupling such as orthogonal frequency division multiplexing (OFDM), frequency-shift keying (FSK), frequency selective digital transmission (FSDT), and wideband signaling (WBS) are explained below. The OFDM-based BCC architecture can transmit at a high data rate. However, the chip size and power consumption are quite large due to the inverse Fourier transform and Viterbi decoder [3]. The FSK-based BCC architecture transmits digital signals by changing the discrete frequency of the carrier signals and using the two frequencies to represent one or zero. However, this modulation requires a specific frequency band that can be easily interfered with by other devices using the same frequency band [4].

In an FSDT-based BCC architecture, the data are distributed over some frequencies, which are used for data transmission. With Walsh codes, the FSDT transceiver can achieve a high data rate. However, this requires a high signal-to-noise ratio (SNR), which is challenging to realize in practice [5]. The WBS BCC architecture has low complexity, low power consumption, does not require complex modulation, and requires a small chip area [6, 7]. However, due to the human body antenna effects, many devices in the environment, such as cordless phones and FM

#### 978-1-6654-0921-6/22/\$31.00 @2022 IEEE

This work was supported in part by the Ministry of Science and Technology of Taiwan under Grant MOST-110-2221-E-194-045- and was financially/partially supported by the Advanced Institute of Manufacturing with High-tech Innovations (AIM-HI) from The Featured Areas Research Center Program within the framework of the Higher Education Sprout Project by the Ministry of Education (MOE) in Taiwan.

radios, can cause tremendous data jitter. Therefore, a clock and data recovery (CDR) circuit that has good jitter tolerance is needed.

In this paper, a WBS BCC transceiver with a 16x oversampling CDR is presented. The proposed transceiver is implemented in a TSMC 90nm CMOS process, and the energy/bit is 0.34nJ/b (TX) and 0.4654nJ/b (RX) at 5Mbps. Moreover, the bit error rate (BER) is less than  $10^{-9}$ . Section II describes the architecture of the proposed BCC TX, and Section III explains the design of the BCC RX. Then Section IV shows the experimental results. Finally, a conclusion is given in Section V.

### II. PROPOSED TX ARCHITECTURE

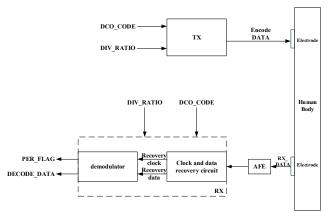

Fig. 1. The overall architecture of the proposed BCC transceiver.

Figure 1 shows the overall architecture of the proposed BCC transceiver. First, the DCO\_CODE and the DIV\_RATIO of TX and RX are set to the same value. Next, the TX\_Modulator generates the data to be transmitted, and the data are encoded by the convolutional encoder and the NRZI encoder, then the data are transmitted through the human body. Then RX\_DATA is amplified by the analog frontend (AFE) circuits. Next, the oversampling clock samples the amplified signal, and the CDR circuit recovers the data. Next, the RX\_Modulator decodes the recovered data and verifies the correctness of the transmission using the CRC32 code. Finally, the packet error rate is calculated to show the BER performance.

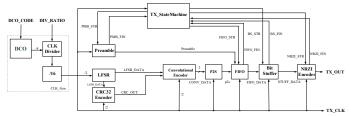

Fig. 2. The block diagram of the proposed BCC transmitter.

Figure 2 shows the block diagram of the proposed BCC transmitter. First, a pattern generator with a linear feedback shift register (LFSR) generates random data to test the BCC. Then, the CRC32 encoder generates the corresponding CRC32 check code.

The convolutional encoder encodes the random data and CRC32 check code, and the encoded data is 2-bit symbols, so the parallel-to-serial module is used to serialize the encoded data. Then, the first-in-first-out (FIFO) block arranges the preamble bits, the start-fame delimiter (SFD), the convolutionally encoded data, and the guard bits into the packet format. The random data may have the longest 19 consecutive identical bits (CIDs). Therefore, the bit stuffer inserts 0 to increase data transitions and avoid burst errors. For the proposed BCC transceiver, the value of the CID can be 2, 3, or 4. Then the data packets are sent with non-return to zero inverted (NRZI) modulation. If the input for the NRZI encoder is 0, the output is inverted. Conversely, if the input is 1, the NRZI encoder retains the output state.

A packet consists of 20 preamble bits for synchronization, 8 start frame delimiter (SFD) bits to detect the start of the packet, 2,000 data bits, 32 bits of CRC32 check code, and the guard bits. The data are encoded with the convolutional code, which has a code rate of 1/2 so that 1,000 bits of data with one packet. The guard bits are intended for the Viterbi decoder, and the length of the guard bits depends on the constraint length of the convolutional code. The convolutional code format can be expressed as (m, n, k), where m is the number of outputs, n is the number of inputs, and k is the constraint length. The longer the constraint length is proportional to the circuit complexity. In this paper, the coded format is (2, 1, 7).

#### III. PROPOSED RX ARCHITECTURE

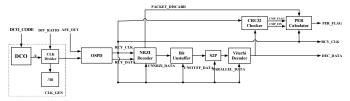

Fig. 3. The block diagram of the proposed BCC receiver.

Figure 3 shows the block diagram of the proposed BCC receiver. It consists of a DCO, clock dividers, an oversampling phase detector (OPSD), the NRZI decoder, a bit unstuffer, a serial-parallel module (s2p), a Viterbi decoder, a CRC32 checker, and a PER calculator. The clock generated by the DCO is used to oversample the AFE OUT, which contains the received data preamplified by the AFE circuit. The OPSD module recovers the data and the clock, and then the system uses RCY CLK as the clock for the other modules. The NRZI decoder decodes RCY DATA and also detects the SFD of the packet. If the SFD cannot be detected, this packet is discarded. After the NRZI decoder, the bit unstuffer removes the data inserted on the transmit side and then converts the serial data to 2-bit parallel data since the Viterbi decoder requires 2-bit data for input. Finally, the DEC DATA is sent to the CRC32 checker to check whether the data are correct or not. The result is sent to the

PER calculator, and the PER calculator outputs the PER\_FLAG to present the performance of the BCC transceiver.

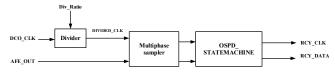

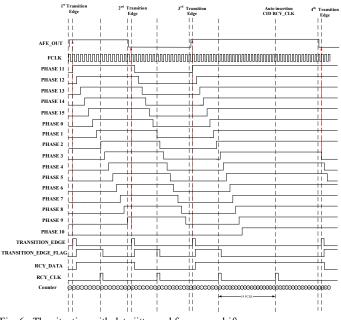

The block diagram of OPSD is shown in Figure 4. The DCO\_CLK is divided by the divider, and the DIVIDED\_CLK is used to oversample the AFE\_OUT. The DIVIDED\_CLK generates sixteen phases, and the OPSD\_STATEMACHINE restores the clock and data.

Fig. 4. The block diagram of the OPSD.

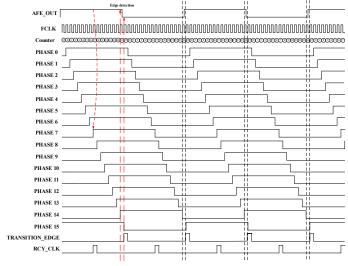

First, the situation without data jitter and frequency drift is considered, as shown in Figure 5. The AFE OUT is oversampled by sixteen phases (PHASE0 to PHASE15). If the data sampled by the adjacent phases are different, there is a data transition. The ideal data transition occurs when the counter value is 15. However, there are interferences and frequency drift in body channel communication between TX and RX so that the AFE OUT may have data jitter and frequency drift. Figure 6 shows the situation with data jitter and frequency drift. When a data transition occurs, the TRANSITION EDGE is set to "1" for one FCLK period, and the counter is set to zero. When the counter value becomes 5, the first RCY CLK is triggered, and the counter is reset to zero. If the counter continues counting to 17 and no data transition is detected, RCY CLK is triggered at this time, and the counter is reset to zero. Typically RCY CLK is triggered when the counter is at 5. The reason for the values 5 and 17 is that the rising edge of RCY CLK is in the middle of 16 phases when the data transition is detected and the counter is at 5, and the reason for counting up to 17 is that there are 16 phases in a symbol.

Fig. 5. The situation without data jitter and frequency drift.

The demodulator shown in Figure 3 consists of the NRZI decoder and the bit unstuffer. The NRZI decoder continues to

decode the incoming RCY\_DATA and also detects whether the data contains the SFD or not. If the SFD is not included in the data, the PACKET\_DISCARD signal is set to 1. Thereupon UNNRZI\_DATA becomes zero, and the packet is discarded. If an SFD is detected, the bit unstuffer removes the zero inserted by the bit stuffer on the TX side. Finally, the UNSTUFF\_DATA are sent to the S2P module and then to the Viterbi decoder.

Fig. 6. The situation with data jitter and frequency drift.

The Viterbi algorithm is used in this work to decode the convolutional codes transmitted by the transmitter. First, the Viterbi algorithm can find the most likely sequence in the retrieved data called the Viterbi path. Then, it traces back the path, finds out the decoded data, and corrects the erroneous data.

### **IV. EXPERIMENTAL RESULTS**

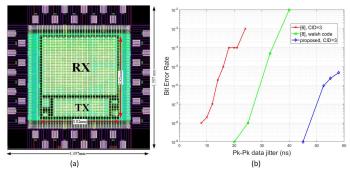

Fig. 7. (a) The layout of the BCC transceiver and (b) BER performance.

The layout of the BCC transceiver chip is shown in Figure 7(a). The test chip is implemented in TSMC 90nm CMOS process with a 1.0 V power supply. The chip size including I/O pads is 1357  $\mu$ m × 1357  $\mu$ m, and the core size is 820  $\mu$ m × 820  $\mu$ m. The operating range of this BCC transceiver is between 1Mbps and 5Mbps. The power consumption without the AFE

#### TABLE I COMPARISON TABLE

|                         | [9] TBioCAS'19 | [10] EMBC'17                  | [11] IEEE Sensor's 15 | [8] ICCETW'18              | [3] JSSC'17          | This work                                  |

|-------------------------|----------------|-------------------------------|-----------------------|----------------------------|----------------------|--------------------------------------------|

| Process                 | N/A            | Texas Instruments<br>TM4C123G | 180nm CMOS            | FPGA                       | 65nm CMOS            | 90nm CMOS                                  |

| Supply voltage          | 3.7V           | 3.3V                          | 1.2V                  | 1.0V                       | 1.1V                 | 1.0V                                       |

| Communication<br>method | OOK            | N/A                           | FSDT                  | Wideband<br>signal         | 8-P OFDM<br>BPSK     | Wideband<br>signal                         |

| Sensitivity             | N/A            | N/A                           | -65dBm                | -18.87dBm                  | -78dBm               | -18.87dBm                                  |

| Max data rate           | 15kbps         | 500kbps                       | 2.625Mbps             | 3.9Mbps                    | 1Mbps                | 5Mbps                                      |

| Max transmission length | 120cm          | 30cm                          | 120cm                 | 140cm                      | N/A                  | 140cm                                      |

| Power consumption       | 7.95nW         | 4.8mW<br>@9.8kbps             | 1.74mW                | 13.5 W<br>13.7W<br>0.441 W | 1.4mW                | 2.327mW (RX)<br>1.7mW (TX)<br>@5Mbps       |

| Area                    | N/A            | N/A                           | 1.05 mm <sup>2</sup>  | N/A                        | 2.13 mm <sup>2</sup> | 1.842 mm <sup>2</sup>                      |

| BER                     | N/A            | < 10 <sup>-7</sup>            | $< 10^{-2}$ (PER)     | < 10 <sup>-5</sup>         | < 10 <sup>-7</sup>   | < 10 <sup>-9</sup>                         |

| Energy/bit              | 0.53nJ/b       | 500nJ/b @9.8kbps              | 0.66nJ/b              | 7.08µJ/b                   | 1.4nJ/b              | 0.4654nJ/b (RX)<br>0.34nJ/b (TX)<br>@5Mbps |

circuit is 2.327mW (RX) and 1.7mW (TX), respectively.

Figure 7(b) shows the BER performance of the proposed BCC. The bit error rate under different data jitter is simulated. In [6], a referenceless CDR architecture is used in the receiver of the BCC. In [8], the Walsh code is used. The data rate of the proposed design is 5 Mbps, and the CID is set to 3. Due to the convolutional code, the jitter tolerance performance of the proposed BCC transceiver is better than the other two designs.

Table I shows the comparison table with other BCC designs. The proposed BCC transceiver has a relatively high data rate than these works [9,10]. In [3,11], the relatively low sensitivity is achieved, but the data rate is lower than the proposed design. The BER performance of the proposed design is also better than these works [3, 8, 10].

## V. CONCLUSION

In this paper, a BCC transceiver with a 16x oversampling CDR and the convolutional code is presented. The proposed design can provide a maximum data rate of 5Mbps with excellent data jitter tolerance.

#### References

- Maicon D. Pereira, Germán A. Alvarez-Botero, and Fernando Rangel de Sousa, "Characterization and modeling of the capacitive HBC channel," *IEEE Transactions on Instrumentation and Measurement (TIM)*, vol. 64, no. 10, pp. 2626-2635, Oct. 2015.

- [2] Namjun Cho, Jerald Yoo, Seong-Jun Song, Jeabin Lee, Seonghyun Jeon, and Hoi-Jun Yoo, "The human body characteristics as a signal transmission medium for intrabody communication," *IEEE Transactions on Microwave Theory and Techniques*, vol. 55, no. 5, pp. 1080-1086, May 2007.

- [3] Wala Saadeh, Muhammad Awais Bin Altaf, Haneen Alsuradi, and Jerald Yoo, "A pseudo OFDM with miniaturized FSK demodulation body-coupled

communication transceiver for binaural hearing aids in 65 nm CMOS", *IEEE Journal of Solid-State Circuits*, vol. 52, no. 3, pp. 757-768, Mar. 2017.

- [4] Joosung Bae, and Hoi-Jun Yoo, "A 45μW injection-locked FSK wake-up receiver with frequency-to-envelope conversion for crystal-less wireless body area network," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 6, pp. 1351-1360, Jun. 2015.

- [5] Hyungil Park, Ingi Lim, Sungweon Kang, and Whan-woo Kim, "10Mbps human body communication SoC for BAN," in Proceedings of 2015 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Oct. 2015, pp. 149-153.

- [6] Ching-Che Chung, Duo Sheng, Ming-Chieh Li, and Yi-Che Tsai, "A fast phase tracking reference-less all-digital CDR circuit for human body channel communication," *Microelectronics Journal*, vol. 84, pp. 87-95, Feb. 2019.

- [7] Ching-Che Chung, Chi-Tung Chang, and Chih-Yu Lin, "A 1 Mb/s 40 Mb/s human body channel communication transceiver," in Proceedings of International Symposium on VLSI Design, Automation, and Test (VLSI-DAT), Apr. 2015.

- [8] Ching-Che Chung, Ru-Hua Chang, and Ming-Hsuan Li, "An FPGA-based transceiver for human body channel communication using Walsh codes," in Proceedings of IEEE International Conference on Consumer Electronics – Taiwan (ICCE-TW), May 2018.

- [9] Jinxi Xiang, Yonggui Dong, Xiaohui Xue, and Hao Xiong, "Electronics of a wearable ECG with level crossing sampling and human body communication," *IEEE Transaction on Biomedical Circuits and Systems*, vo. 13, no.1, pp. 68-79, Feb. 2019.

- [10] Shovan Maity, Debayan Das, and Shreyas Sen, "Wearable health monitoring using capacitive voltage-mode human body communication," in Proceedings of Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Jul. 2017.

- [11] Yu Lin Tsou, Cihun-Siyong Alex Gong, Nai Chen Cheng, Yu Lee, and Christina F. Jou, "Integrated biosensing platform based on a 1.74-mW -90-dBm sensitivity dual- mode-operation receiver for IEEE 802.15.6 human body communication standard," *IEEE Sensors Journal*, vol. 15, pp. 3317-3327, Jun. 2015.