# A Low-Power and Small-Area All-Digital Spread-Spectrum Clock Generator in 65nm CMOS Technology

Ching-Che Chung<sup>1</sup>, Duo Sheng<sup>2</sup>, and Wei-Da Ho<sup>1</sup>

<sup>1</sup> Department of Computer Science and Information Engineering, National Chung Cheng University,

No. 168 University Rd., Min-Hsiung, Chia-Yi, Taiwan

<sup>2</sup> Department of Electrical Engineering, Fu Jen Catholic University,

No. 510 Chung-Cheng Rd. Hsin-Chung, Taipei, Taiwan.

Email: wildwolf@cs.ccu.edu.tw

Abstract-In this paper, a low-power and small-area all-digital spread spectrum clock generator (ADSSCG) is presented. The proposed ADSSCG can provide a programmable spreading ratio. In order to maintain the frequency stability while performing triangular modulation, a fast frequency and phase relock mechanism is proposed to overcome the process, voltage, and temperature (PVT) variations. The proposed ADSSCG is implemented in a standard performance 65nm CMOS process, and the active area is  $100\mu m \times 100\mu m$ . The simulation results show that the electromagnetic interference (EMI) reduction is 22.6dB with 1.3% spreading ratio at 270MHz and 18.9dB with 0.45% spreading ratio at 162MHz. The power consumption is 229µW at 270MHz with 1.0V power supply. Besides, the proposed ADSSCG is implemented with standard cells, and thus it can be easily ported to different processes in a very short time. Therefore, the proposed ADSSCG is suitable for system-on-chip (SoC) applications.

#### I. INTRODUCTION

In recent years, the issue of electromagnetic interference (EMI) in electronic products is highly discussed. There are many techniques provided to reduce EMI, such as shielding or low-voltage differential clocking. However, the shielding technique is cost-expensive, and the other one has a complex routing. Spread spectrum clock generator (SSCG) [1]-[7] is an appropriate solution to effectively reduce EMI with low hardware cost. There are several modulation methods of SSCG, two popular methods are direct modulation on voltage-controlled oscillator (VCO) [1]-[2], and modulation on frequency divider with a delta-sigma modulator (DSM) [7]. However, direct modulation on VCO usually requires a very large on-chip capacitor as a loop filter and occupies a large chip area. The other method, modulation on frequency divider, due to the quantization noise of divider, also requires a large on-chip capacitor. Since the MOS capacitor in 65nm CMOS process has serious leakage current problem, these analog approaches must be redesigned as technology migrates.

To reduce the area of the loop filter in analog approaches, alldigital spread spectrum clock generators (ADSSCGs) [3]-[6] are proposed to reduce the capacitor area. The ADSSCG uses a digital loop filter to replace the passive loop filter in analog approaches, and therefore, it can have a much smaller area than conventional analog SSCGs. However, due to the resolution limitation of the digital controlled oscillator (DCO), the ADSSCG [5]-[6] often needs to use a larger spread ratio to achieve the same EMI reduction as compared with analog SSCGs. As a result, the jitter performance of the ADSSCGs may be worse than analog SSCGs. In addition, the design challenge to design an ADSSCG is to maintain frequency stability (i.e. average frequency) while performing spread spectrum operation with process, voltage, and temperature (PVT) variations. An ADSSCG also needs to provide a programmable spreading ratio for trade-off between the jitter performance and the EMI reduction.

Furthermore, the non-monotonic DCO response will greatly influence the performance of the EMI reduction. Thus, in [9], a builtin self-calibration circuit for monotonic DCO design is presented. In addition, an interpolation-type DCO, which the fine-tuning stage implemented with interpolator circuits, can provide a monotonic response between the DCO control code and the output frequency is presented in [8][10]. The triangular modulation is often used in the SSCG. However, the triangular modulation makes it difficult to maintain the frequency stability of the output clock. Thus, in [5], a division triangular method is proposed to overcome this problem. However, the proposed ADSSCG [5] has a large cycle-to-cycle jitter. In addition, it can not be applied to the transceiver design with SSCG, such as the serial advanced technology attachment (SATA), since it is very difficult to track the frequency deviations of the data with division triangular method.

In this paper, an ADSSCG with direct modulation on the DCO is presented. The proposed ADSSCG can perform fast frequency and phase tracking during the triangular modulation. A DSM with the DCO can enhance the DCO resolution, and thus, the direct modulation on the DCO can generate an accurate triangular modulation on the output frequency. As a result, the proposed ADSSCG can provide a better EMI reduction with a smaller spreading ratio. In order to reduce the overall power consumption of the ADSSCG, the low-power monotonic DCO is designed. The proposed ADSSCG is implemented with standard cells, and therefore, it is very suitable for system-on-chip (SoC) applications.

The rest of the paper is organized as follows: the proposed ADSSCG architecture is presented in Section II. The fast frequency and phase maintenance mechanism is discussed in Section III. The monotonic DCO circuit design is discussed in Section IV. Section V shows the experimental results of the proto-type chip. Finally, Section VI concludes with a summary.

# II. ARCHITECTURE OVERVIEW

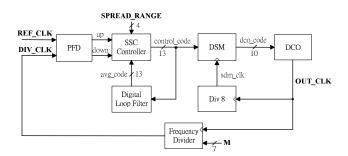

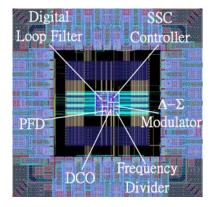

Fig. 1 shows the block diagram of the proposed ADSSCG. The ADSSCG is composed of a phase and frequency detector (PFD), a spread spectrum clock (SSC) controller, a digital loop filter (DLF), a delta-sigma modulator (DSM), a monotonic DCO, and a frequency divider. The SSC controller directly controls the DCO control code (control\_code) to perform center-spread triangular modulation on the output frequency. According to the user-defined spreading range (SPREAD\_RANGE), the SSC controller modulates the output frequency to achieve the corresponding spreading ratio.

This work was supported in part by the National Science Council of Taiwan, R.O.C., under Grant NSC100-2221-E-194-051.

To generate a smooth triangular modulation profile, the DCO resolution is further enhanced by employing a DCO dithering scheme through a 3-bit first-order DSM. The integral part of the DCO control code has 10 bits, and the fractional part of the DCO control code has 3 bits. The operation speed of the DSM is the output clock frequency divided by 8. Due to the enhancement of the DCO equivalent resolution, the proposed ADSSCG can provide a better EMI reduction with a smaller spreading ratio.

FIGURE 1. THE PROPOSED ADSSCG.

The digital loop filter [10] is applied in the ADSSCG to generate a stable average frequency to eliminate the jitter effects of the reference clock. The loop filter can generate a baseline DCO control code (avg\_code) for the SSC controller. Thus, the SSC controller can keep updating the triangular modulation profile with PVT variations.

# III. FREQUENCY AND PHASE MAINTENANCE

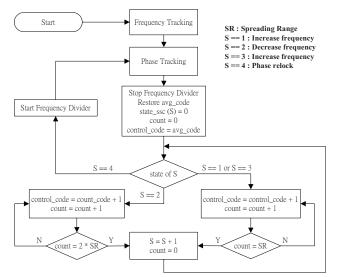

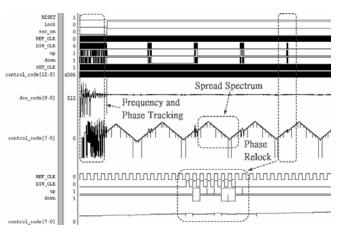

To maintain the frequency stability while performing spread spectrum, a fast frequency and phase relock mechanism is presented, as shown in Fig. 2. After system is reset, the ADSSCG performs frequency and phase tracking and operates as a normal phase-locked loop (PLL). After frequency and phase tracking is completed, the SSC controller starts the triangular modulation. There are four spread spectrum states (state\_ssc). The first three states are used to modulate the DCO control code to generate a triangular profile. In the fourth state, the SSC controller performs the fast frequency and phase relock to maintain the frequency stability of the output clock. In Fig. 2, the user-defined spreading range (SR) is used to control the triangular profile, and therefore the spreading ratio can be easily adjusted.

FIGURE 2. THE FLOWCHART OF THE PROPOSED ADSSCG.

The frequency divider is stopped during the triangular profile generation, as shown in Fig. 3. Thus the ADSSCG becomes an openloop while performing spread spectrum generation. Subsequently, at the fourth state of state scc, the frequency divider is enabled to perform frequency and phase tracking again. When the frequency divider is enabled, the phase error between the reference clock (REF CLK) and the divided clock (DIV CLK) is eliminated. Then, the SSC controller performs frequency and phase tracking to maintain the frequency stability of the output clock. The digital loop filter will update the baseline DCO control code (avg code) during the frequency and phase relock process. After the phase relock process is completed, the SSC restores the baseline DCO control code and starts the triangular modulation again from the current baseline DCO control code. The fast frequency and phase relock mechanism is repeated in the end of each triangular profile to ensure the frequency stability of the output clock.

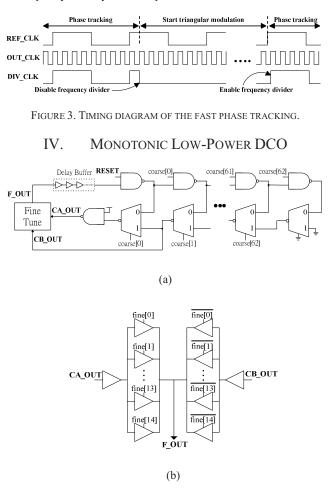

FIGURE 4. THE PROPOSED DCO:

(a) COARSE-TUNING STAGE (b) FINE-TUNING STAGE.

The monotonic response between the DCO control code and the output frequency is an important issue in ADSSCG design. The nonmonotonic DCO response will result in poor EMI reduction. Therefore, a monotonic low-power DCO circuit [8] is presented, as shown in Fig. 4. The proposed DCO is implemented with standard cells. The DCO is composed of a ladder-shaped coarse-tuning stage and an interpolating fine-tuning stage. The coarse-tuning circuit has 64 coarse-delay cells (CDCs) and one NAND gate, as shown in Fig. 4(a). This CDC is combined with one NAND gate and one inverted MUX. Hence, the coarse-tuning resolution is equal to the delay time of one CDC. In order to design a low power DCO, the DCO coarsetuning code (coarse[62:0]) is used to control the NAND gate. This approach can turn off unnecessary NAND gates to reduce power consumption.

The fine-tuning stage is used to provide a fine DCO resolution in the cascaded DCO architecture. However, the total delay controllable range of the fine-tuning stage must be equal to the coarse-tuning resolution to ensure the monotonic DCO response. Fig. 4 (b) is the fine-tuning stage of the proposed DCO. The fine-tuning stage is composed of two parallel connected tri-state buffer arrays operating as an interpolator circuit. When there are more tri-state buffers turned on in the left side array, the output (F OUT) will be more close to the CA OUT. Oppositely, when there are more tri-state buffers turned on in the right side array, the output will be more close to the CB OUT. The delay difference between CA OUT and CB OUT is the delay time of one CDC, as shown in Fig. 4 (a). Therefore, a finetuning stage with the average resolution equal to 1/16 of the coarsetuning resolution can be achieved. As a result, the non-monotonic problem in conventional cascaded DCO architecture can be avoided in the proposed DCO.

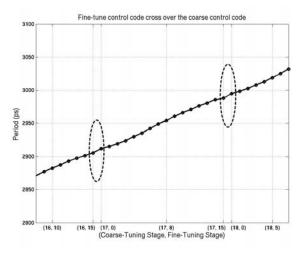

The frequency range of the proposed DCO is from 138MHz to 624MHz with 87ps coarse-tuning resolution and 5.43ps fine-tuning resolution. With the enhancement of delta-sigma modulator, the equivalent DCO resolution is 0.679ps. The power consumption of the proposed DCO is 190.6 $\mu$ W at 624MHz. Fig. 5 shows the simulation results of the proposed DCO, and the DCO has a monotonic response when the coarse-tuning control code is switched.

FIGURE 5. FINE-TUNING CODE CROSS OVER 2 COARSE-TUNING CODE.

# V. EXPERIMENTAL RESULTS

The proposed ADSSCG is implemented in a standard performance (SP) 65nm CMOS process with 1.0V power supply. Fig. 6 shows the layout of the ADSSCG. The active area is  $100\mu m \times 100\mu m$ .

The simulation result of the proposed ADSSCG is shown in Fig. 7. After system is reset, the ADSSCG performs frequency and phase tracking until the PLL is locked. After that, the SSC function is turned on, and the frequency divider is stopped during the triangular profile generation. The spreading ratio is dependent on the user-defined spreading range. As compared with other SSCG [1]-[3],[7], the proposed ADSSCG operates as an open-loop while performing

spread spectrum generation. Therefore, a perfect triangular modulation can be achieved without the disturbance comes from the PFD. However, the reference clock jitter effects and the PVT variations will influence the frequency stability of the output clock. Thus, in the proposed ADSSCG, at the end of the triangular modulation, the SSC controller performs a fast frequency and phase relock to maintain the frequency stability. In addition, the loop filter can filter out the reference clock jitter effects during the relock process.

FIGURE 6. LAYOUT OF THE PROPOSED ADSSCG.

FIGURE 7. SIMULATION RESULTS OF THE PROPOSED ADSSCG.

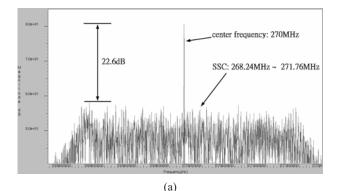

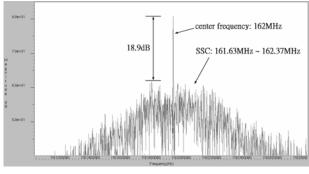

Fig. 8 shows the simulated spectra of the output clock with center spread at 270MHz and 162MHz, respectively. The EMI reduction is 22.6dB at 270MHz with 1.3% spreading ratio, as shown in Fig. 8(a). Fig. 8(b) shows the 18.9dB EMI reduction is achieved at 162MHz with 0.45% spreading ratio. Table I lists comparison results with the state-of-the-art SSCGs. The proposed ADSSCG can provide a better EMI reduction with a smaller spreading ratio. In addition, the proposed low-power monotonic DCO also reduces the overall power consumption of the ADSSCG, and the proposed ADSSCG has smallest area as compared to the existing SSCGs.

# VI. CONCLUSION

In this paper, we proposed a low-power and small-area all-digital spread-spectrum clock generator with programmable spreading ratio for SoC applications. The proposed ADSSCG can generate a perfect triangular modulation without the disturbance comes from the PFD, and thus, the higher EMI reduction can be achieved with a smaller spreading ratio. As a result, the jitter performance of the ADSSCGs is better than the other SSCGs with a much larger spreading ratio to

| Parameter    | Modulation<br>profile  | Modulation method              | EMI reduction                                                 | Output<br>frequency   | Process | Area                                        | Power consumption                     |

|--------------|------------------------|--------------------------------|---------------------------------------------------------------|-----------------------|---------|---------------------------------------------|---------------------------------------|

| Proposed     | Triangular             | All-Digital                    | 22.6 dB (1.3%)<br>(@270 MHz)<br>18.9 dB (0.45%)<br>(@162 MHz) | 162 MHz ~<br>270 MHz  | 65nm    | 0.01 mm <sup>2</sup>                        | 229µW<br>(@270MHz)                    |

| JSSC'03 [1]  | Triangular             | Analog PLL<br>(VCO modulation) | 11dB (2.5%)<br>(@266 MHz)                                     | 66 MHz ~<br>266 MHz   | 0.35µm  | 2.0 mm <sup>2</sup>                         | 300mW<br>(@266MHz)                    |

| TCAS2'11 [2] | Triangular             | Analog PLL<br>(VCO modulation) | 8.75dB (0.5%)<br>(@ 270MHz)                                   | 162 MHz ~<br>270 MHz  | 0.18µm  | 1.8 mm <sup>2</sup>                         | 19mW<br>(@270MHz)                     |

| JSSC'09 [3]  | Triangular             | All-Digital                    | 10.48dB (0.5%)<br>(@1.5GHz)                                   | 1.5 GHz               | 0.18µm  | $0.2 \text{ mm}^2$                          | 15mW<br>(@1.5GHz)                     |

| JSSC'10 [4]  | Arbitrary              | Digital Delay-Line             | 20.5dB (6%)<br>(@750MHz)                                      | 180 MHz ~<br>1.27 GHz | 65nm    | 0.044 mm <sup>2</sup><br>(excluding<br>PLL) | 44mW<br>(@1.27GHz)<br>(excluding PLL) |

| TVLSI'11 [5] | Division<br>triangular | All-Digital                    | 15dB (10%)<br>(@27MHz)<br>9.2dB (1%)<br>(@54MHz)              | 27 MHz ~<br>54 MHz    | 0.18µm  | 0.156 mm <sup>2</sup>                       | 1.2mW<br>(@54MHz)                     |

TABLE I. PERFORMANCE COMPARISONS

achieve the same EMI reduction. The power consumption of the proposed ADSSCG is  $229\mu$ W at 207MHz. Moreover, the proposed ADSSCG has a good portability. Therefore, it is very suitable for system level integration in SoC era.

(b)

Figure 8. Simulated spectra of (a) 270MHz with 1.3% spreading ratio and (b) 162MHz with 0.45% spreading ratio.

### ACKNOWLEDGMENT

The authors would like to thank their colleagues in S3 Lab of National Chung Cheng University for many fruitful discussions. The shuttle program supported by UMC is acknowledged as well.

#### References

- Hsiang-Hui Chang, I-Hui Hua, and Shen-Iuan Liu, "A spreadspectrum clock generator with triangular modulation," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 4, pp. 673-676, Apr. 2003.

- [2] Won-Young Lee and Lee-Sup Kim, "A spread spectrum clock generator for DisplayPort main link," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 58, no. 3, pp. 361-635, Jun. 2011.

- [3] Sheng-You Lin and Shen-Iuan Liu, "A 1.5 GHz all-digital spread-spectrum clock generator," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 11, pp. 3111-3119, Nov. 2009.

- [4] Davide De Caro, et al., "A 1.27 GHz, all-Digital spread spectrum clock generator/synthesizer in 65nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 5, pp. 1048-1060, May 2010.

- [5] Duo Sheng, Ching-Che Chung, and Chen-Yi Lee, "A low-power and portable spread spectrum clock generator for SoC applications," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 19, no. 6, pp. 1113-1117, Jun. 2011.

- [6] Duo Sheng, Ching-Che Chung, and Chen-Yi Lee, "An all digital spread spectrum clock generator with programmable spread ratio for SoC applications," *in Proceedings of IEEE Asia Pacific Conference on Circuits and Systems (APCCAS)*, Nov. 2008, pp. 850-853.

- [7] Ching-Yuan Yang, Chih-Hsiang Chang, and Wen-Ger Wong, "A  $\Delta$ - $\Sigma$  PLL-based spread-spectrum clock generator with a ditherless fractional topology," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 56, no. 1, pp. 51-59, Jan. 2009.

- [8] Duo Sheng and Jhih-Ci Lan, "A monotonic and low-Power digitally controlled oscillator with portability for SoC applications," in Proceedings of IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 2011.

- [9] Ching-Che Chung, Chiun-Yao Ko, and Sung-En Shen, "A builtin self calibration circuit for monotonic digitally controlled oscillator design in 65nm CMOS technology, " *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 58, no. 3, pp. 149-153, Mar. 2011.

- [10] Ching-Che Chung and Chiun-Yao Ko, "A fast phase tracking ADPLL for video pixel clock generation in 65nm CMOS technology," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 10, pp. 2300-2311, Oct. 2011.